Rainbow Electronics AT45DB021D User Manual

Page 34

34

3638K–DFLASH–11/2012

AT45DB021D

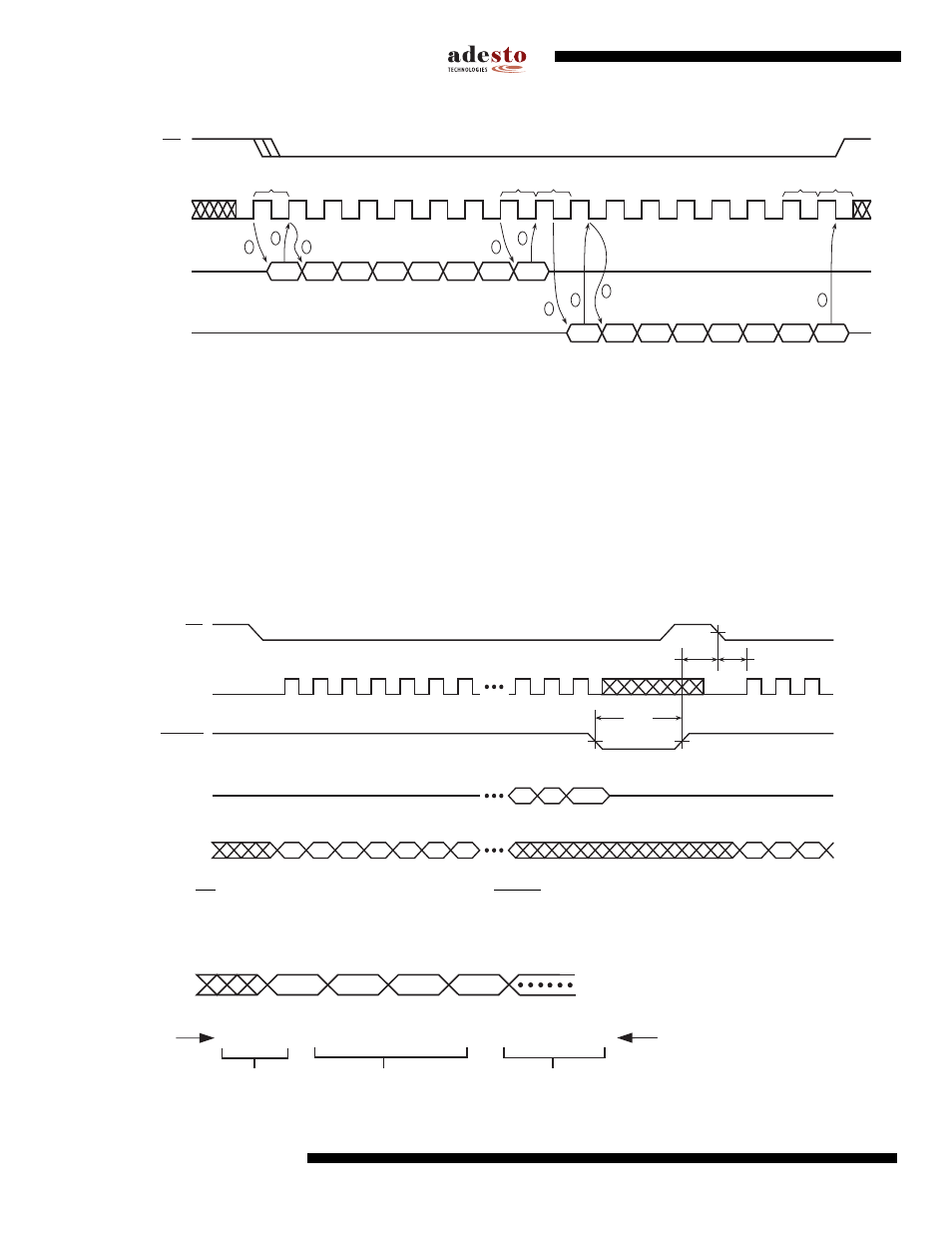

Figure 17-5. RapidS Mode

Figure 17-6. Reset Timing

Note:

The CS signal should be in the high state before the RESET signal is deasserted

Figure 17-7. Command Sequence for Read/Write Operations for Page Size 256-Bytes (Except Status Register

Read, Manufacturer and Device ID Read)

SCK

MOSI

MISO

1

2 3 4 5 6 7

8 1

2 3 4 5 6 7

8

MOSI = Master Out, Slave In

MISO = Master In, Slave Out

The Master is the host controller and the Slave is the DataFlash

The Master always clocks data out on the rising edge of SCK and always clocks data in on the falling edge of SCK.

The Slave always clocks data out on the falling edge of SCK and always clocks data in on the rising edge of SCK.

A. Master clocks out first bit of BYTE-MOSI on the rising edge of SCK

B. Slave clocks in first bit of BYTE-MOSI on the next rising edge of SCK

C. Master clocks out second bit of BYTE-MOSI on the same rising edge of SCK

D. Last bit of BYTE-MOSI is clocked out from the Master

E. Last bit of BYTE-MOSI is clocked into the slave

F.

Slave clocks out first bit of BYTE-SO

G. Master clocks in first bit of BYTE-SO

H. Slave clocks out second bit of BYTE-SO

I.

Master clocks in last bit of BYTE-SO

A

B

C

D

E

F

G

1

H

BYTE-MOSI

MSB LSB

BYTE-SO

MSB LSB

Slave

CS

I

CS

SCK

RESET

SO (OUTPUT)

HIGH IMPEDANCE

HIGH IMPEDANCE

SI (INPUT)

tRST

tREC

tCSS

SI (INPUT)

CMD

8 bits

8 bits

8 bits

Page Address

(A17 - A8)

X X X X X X X X

X X X X X X X X

LSB

X X X X X X X X

Byte/Buffer Address

(A7 - A0/BFA7 - BFA0)

MSB

6 Don’t Care

Bits