Pin configurations and pinouts – Rainbow Electronics AT45DB161D User Manual

Page 2

2

3500O–DFLASH–11/2012

AT45DB161D

operation. Unlike conventional Flash memories that are accessed randomly with multiple address lines and a

parallel interface, the Adesto DataFlash

®

uses a RapidS serial interface to sequentially access its data. The simple

sequential access dramatically reduces active pin count, facilitates hardware layout, increases system reliability,

minimizes switching noise, and reduces package size. The device is optimized for use in many commercial and

industrial applications where high-density, low-pin count, low-voltage and low-power are essential.

To allow for simple in-system reprogrammability, the AT45DB161D does not require high input voltages for

programming. The device operates from a single power supply, 2.5V to 3.6V or 2.7V to 3.6V, for both the program

and read operations. The AT45DB161D is enabled through the chip select pin (CS) and accessed via a three-wire

interface consisting of the Serial Input (SI), Serial Output (SO), and the Serial Clock (SCK).

All programming and erase cycles are self-timed.

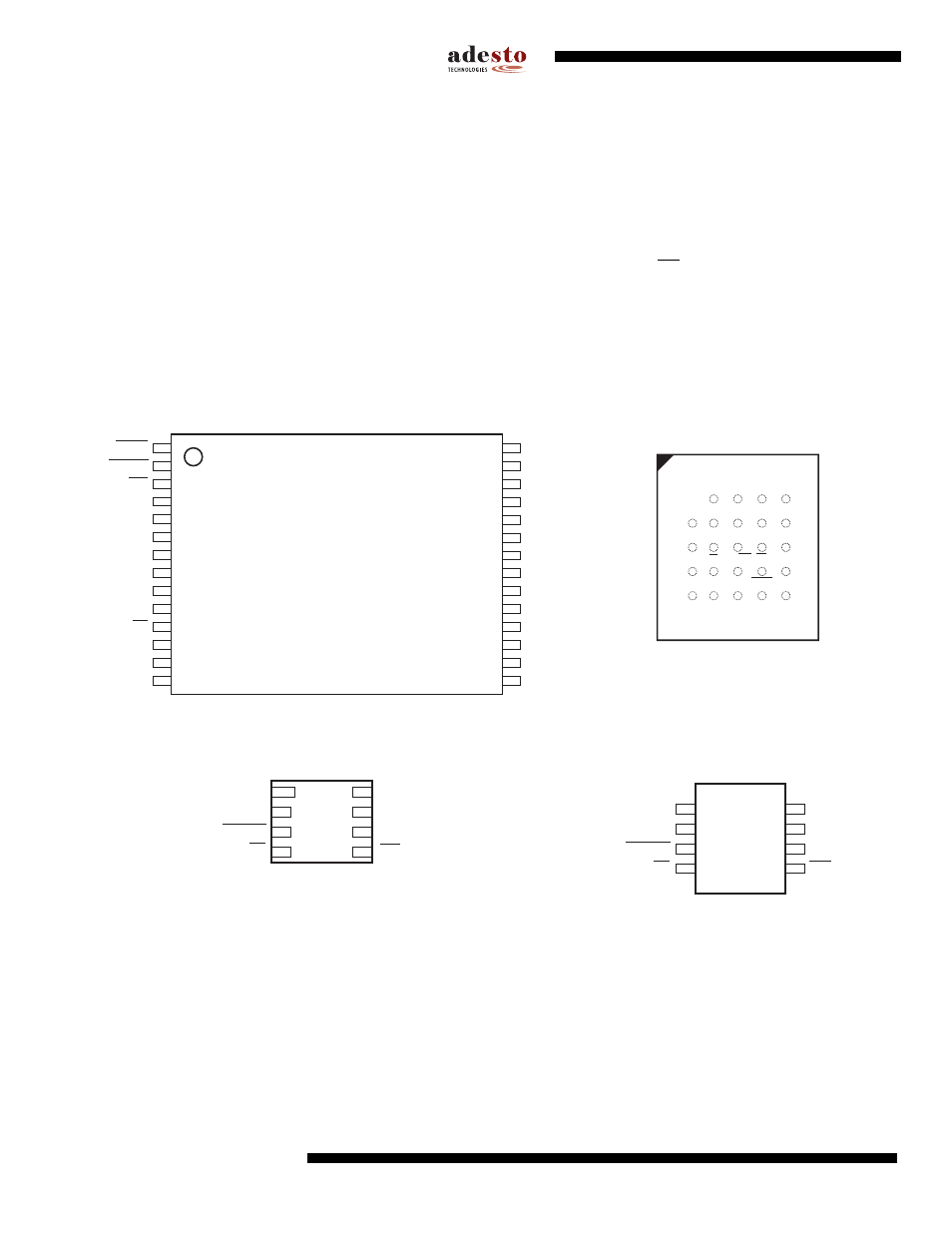

2.

Pin Configurations and Pinouts

Note:

1. The metal pad on the bottom of the MLF package is floating. This pad can be a “No Connect” or connected to GND

Figure 2-1.

TSOP Top View: Type 1

Figure 2-2.

BGA Package Ball-out

(Top View)

Figure 2-3.

MLF (VDFN) Top View

Figure 2-4.

SOIC Top View

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

RDY/BUSY

RESET

WP

NC

NC

VCC

GND

NC

NC

NC

CS

SCK

SI

SO

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

A

B

C

D

E

5

4

3

2

1

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

VCC

GND

SCK

CS

RDY/BSY

WP

SI

SO

RESET

SI

SCK

RESET

CS

SO

GND

VCC

WP

8

7

6

5

1

2

3

4

1

2

3

4

8

7

6

5

SI

SCK

RESET

CS

SO

GND

VCC

WP