Reset timing (inactive clock polarity low shown) – Rainbow Electronics AT45DB011B User Manual

Page 15

15

AT45DB011B

1984E–DFLSH–10/02

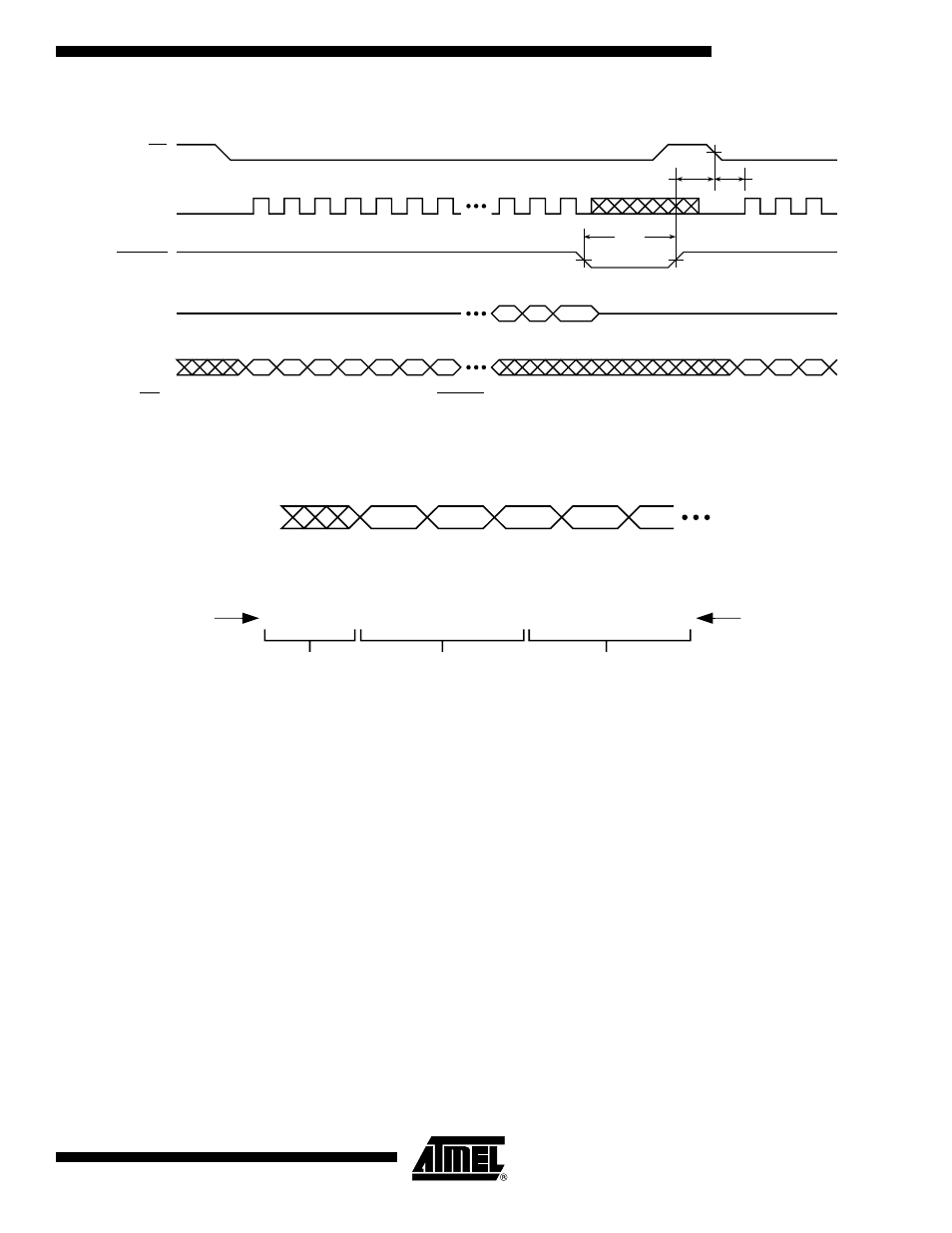

Reset Timing (Inactive Clock Polarity Low Shown)

Note:

The CS signal should be in the high state before the RESET signal is deasserted.

Command Sequence for Read/Write Operations (Except Status Register Read)

Notes:

1. “r” designates bits reserved for larger densities.

2. It is recommended that “r” be a logical “0”.

3. For densities larger than 1M bit, the “r” bits become the most significant Page Address bit for the appropriate density.

CS

SCK

RESET

SO

HIGH IMPEDANCE

HIGH IMPEDANCE

SI

tRST

tREC

tCSS

SI

CMD

8 bits

8 bits

8 bits

MSB

Reserved for

larger densities

Page Address

(PA8-PA0)

Byte/Buffer Address

(BA8-BA0/BFA8-BFA0)

LSB

r r r r

r r X X

X X X X X X X X

X X X X X X X X

See also other documents in the category Rainbow Electronics Storage:

- W27E010 (14 pages)

- W27L520 (16 pages)

- W29EE512 (21 pages)

- W27E512 (16 pages)

- W24100 (11 pages)

- W27E040 (15 pages)

- W25Q32 (60 pages)

- W49L102 (21 pages)

- W29C040 (20 pages)

- W29EE011 (20 pages)

- W49F020 (21 pages)

- W2465 (10 pages)

- W24256 (10 pages)

- W982516CH (43 pages)

- MAX16014 (12 pages)

- W24512A (10 pages)

- W27E020 (14 pages)

- W29C020C (21 pages)

- W25X64 (47 pages)

- W24257 (11 pages)

- W24L257 (10 pages)

- W9864G2GH (48 pages)

- W24L11 (11 pages)

- W27L010 (14 pages)

- W27E520 (16 pages)

- W27LE520 (16 pages)

- W9825G6CH (43 pages)

- W49F002U (23 pages)

- W9864G6GB (47 pages)

- AT45DB642 (71 pages)

- AT45DB642 (37 pages)

- AT45DB161D (51 pages)

- AT27LV040A (12 pages)

- AT29LV010A (15 pages)

- HT24LC08 (11 pages)

- AT29C257 (12 pages)

- AT45DB161B (32 pages)

- AT27C1024 (12 pages)

- AT28BV256 (12 pages)

- AT28C040 (12 pages)

- DS1258Y_AB (9 pages)

- AT28BV64B (12 pages)

- AT27C512R (12 pages)

- DS1220AB_AD (9 pages)