Rx fifo buffered data read, Rf12b – Rainbow Electronics RF12B User Manual

Page 25

RF12B

Note:

The content of the data registers are initialized by clearing bit et.

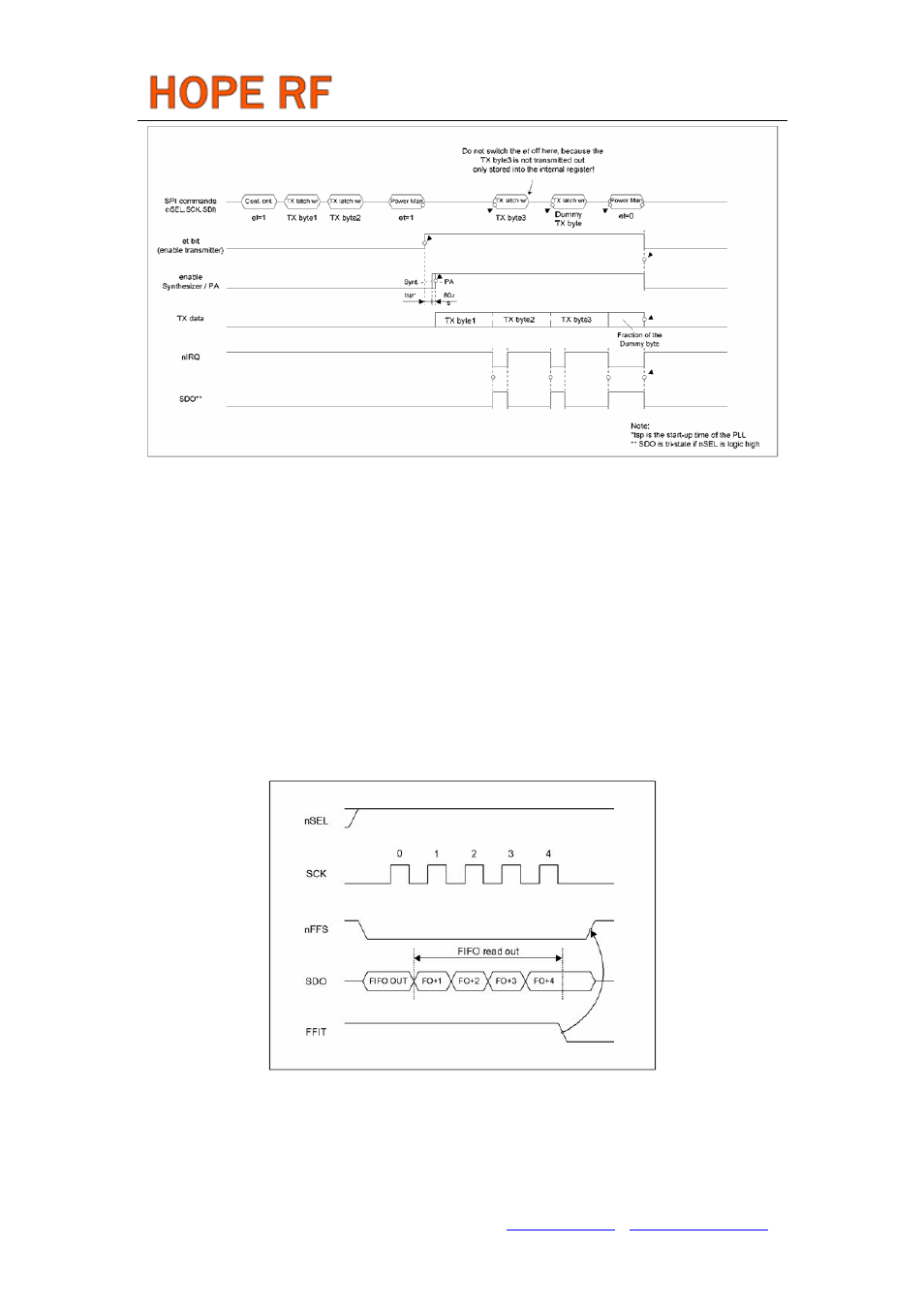

RX FIFO BUFFERED DATA READ

In this operating mode, incoming data are clocked into a 16 bit FIFO buffer. The receiver starts to fill

up the FIFO when the Valid Data Indicator (VDI) bit and the synchron pattern recognition circuit indicates

potentially real incoming data. This prevents the FIFO from being filled with noise and overloading the

external microcontroller.

Interrupt Controlled Mode:

The user can define the FIFO IT level (the number of received bits) which will generate the nFFIT

when exceeded. The status bits report the changed FIFO status in this case.

FIFO Read Example with FFIT Polling

Note

: During FIFO access f

cannot be higher than f /4, where f

SCK

ref

ref

is the crystal oscillator frequency.

When the duty-cycle of the clock signal is not 50% the shorter period of the clk pulse should be at least

2/f second.

ref

Tel: +86-755-86096587 Fax: +86-755-86096602 E-mail: [email protected] http://www.hoperf.com