Applications information, Table 40. register summary (continued) – Rainbow Electronics MAX5971B User Manual

Page 43

______________________________________________________________________________________ 43

MAX5971B

Single-Port, 40W, IEEE 802.3af/at,

PSE Controller with I

2

C

Applications Information

Layout Procedure

Careful PCB layout is critical to achieve high efficiency

and low EMI. Follow these layout guidelines for optimal

performance.

1) Place the high-frequency input bypass capacitor (0.1FF

ceramic capacitor from AGND to V

EE

) and the output

bypass capacitor (0.1FF ceramic capacitor from AGND

to OUTP) as close as possible to the MAX5971B.

2) Use large SMT component pads for power dissipat-

ing devices, such as the MAX5971B and the external

diodes in the high-power path.

3) Use short, wide traces whenever possible for high-

power paths.

4) Use the MAX5971B Evaluation Kit as a design and

layout reference.

5) The EP must be soldered evenly to the PCB ground

plane (V

EE

) for proper operation and power dissipa-

tion. Use multiple vias beneath the EP for maximum

heat dissipation. A 1.0mm to 1.2mm pitch is the

recommended spacing for these vias and should

be plated (1oz copper) with a small barrel diameter

(0.30mm to 0.33mm).

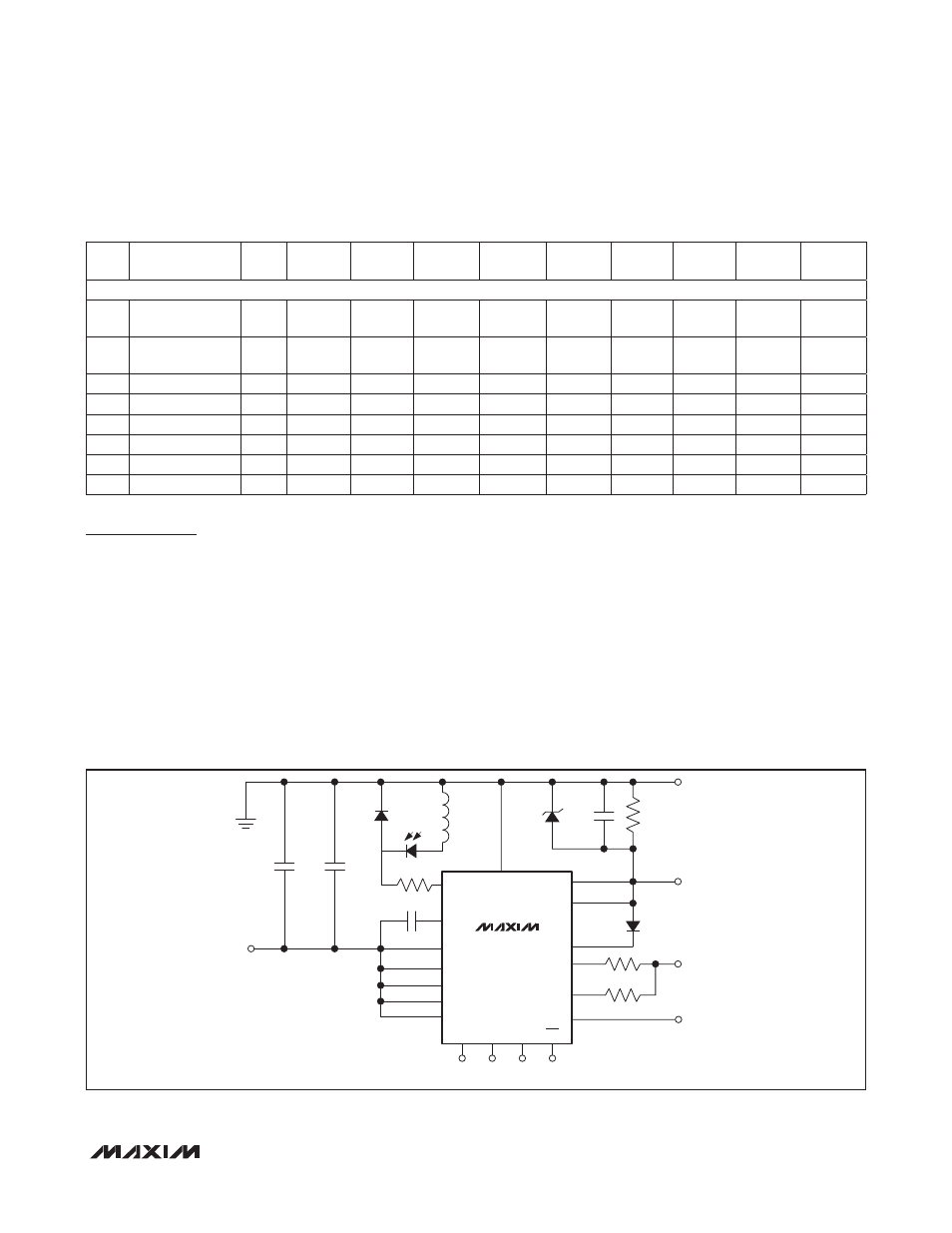

Figure 15. Typical Operating Circuit 1 (DC Load Removal Detection, Internal PWM Enabled for LED Indication, and Class 5

Detection Enabled)

Table 40. Register Summary (continued)

5.1kI

1kI

1kI

2.2MI

0.1µF

100V

SMJ58A

-54V

-54V

47µF

100V

0.1µF

100V

1N4448

1N4448

10mH

1nF

AGND

SERIAL INTERFACE

SDA

SCL

AD0

INT

V

EE

V

EE_DIG

EN

LED

LED

LEGACY

MIDSPAN

OSC

OUT

OUTP

PWMEN

DET

ILIM1

ILIM2

MAX5971B

PSE OUTPUT

ADDR REGISTER NAME

R/W

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

RESET

STATE

CURRENT READOUT

30H Port Current (MSB)

R

IPD[8]

IPD[7]

IPD[6]

IPD[5]

IPD[4]

IPD[3]

IPD[2]

IPD[1]

0000 to

0000

31H Port Current (LSB)

R

Reserved Reserved

Reserved

Reserved

Reserved Reserved Reserved

IPD[0]

0000 to

0000

32H Reserved

—

Reserved Reserved

Reserved

Reserved

Reserved Reserved Reserved

Reserved

—

33H Reserved

—

Reserved Reserved

Reserved

Reserved

Reserved Reserved Reserved

Reserved

—

34H Reserved

—

Reserved Reserved

Reserved

Reserved

Reserved Reserved Reserved

Reserved

—

35H Reserved

—

Reserved Reserved

Reserved

Reserved

Reserved Reserved Reserved

Reserved

—

36H Reserved

—

Reserved Reserved

Reserved

Reserved

Reserved Reserved Reserved

Reserved

—

37H Reserved

—

Reserved Reserved

Reserved

Reserved

Reserved Reserved Reserved

Reserved

—