Rainbow Electronics MAX5971B User Manual

Page 23

______________________________________________________________________________________ 23

MAX5971B

Single-Port, 40W, IEEE 802.3af/at,

PSE Controller with I

2

C

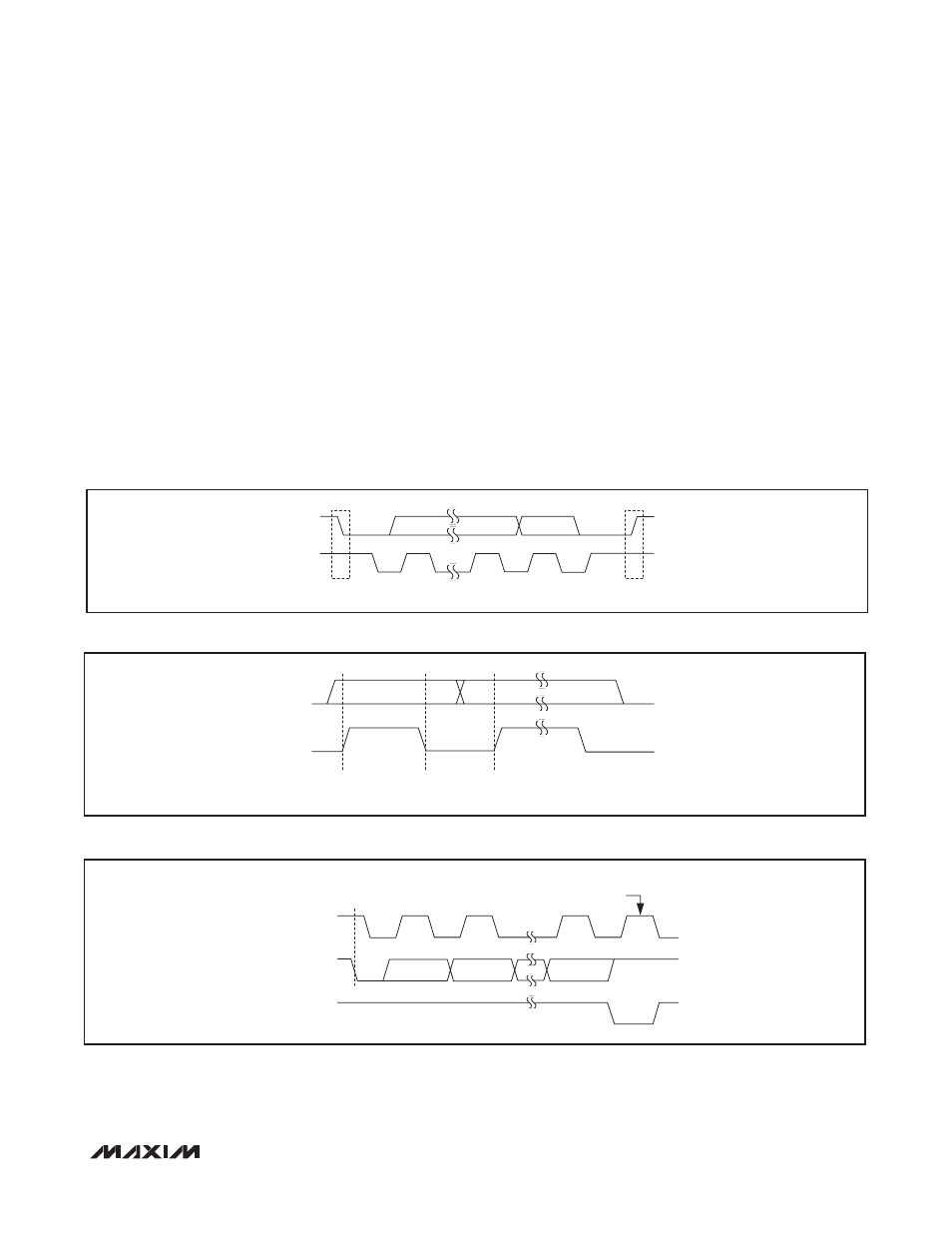

Figure 7. START and STOP Conditions

Figure 8. Bit Transfer

Figure 9. Acknowledge

Serial-Addressing

Each transmission consists of a START condition sent by

a master, followed by the MAX5971B 7-bit slave address

plus R/W bit, a register address byte, one or more data

bytes, and finally a STOP condition.

START and STOP Conditions

Both SCL and SDA remain high when the interface is

not busy. A master signals the beginning of a transmis-

sion with a START condition by transitioning SDA from

high to low while SCL is high. When the master finishes

communicating with the slave, the master issues a STOP

condition by transitioning SDA from low to high while

SCL is high. The stop condition frees the bus for another

transmission (see Figure 7).

Bit Transfer

Each clock pulse transfers one data bit (Figure 8). The

data on SDA must remain stable while SCL is high.

Acknowledge

The acknowledge bit is a clocked 9th bit (Figure 9), which

the recipient uses to handshake receipt of each byte of

data. Thus each byte transferred effectively requires 9

bits. The master generates the 9th clock pulse, and the

recipient pulls down SDA during the acknowledge clock

pulse, so that the SDA line is stable low during the high

period of the clock pulse. When the master transmits to

the MAX5971B, the device generates the acknowledge

bit. When the MAX5971B transmits to the master, the

master generates the acknowledge bit.

SDA

SCL

S

START

STOP

P

SDA

SCL

DATA LINE STABLE;

DATA VALID

CHANGE OF

DATA ALLOWED

SCL

SDA BY

TRANSMITTER

SDA BY

RECEIVER

START

CONDITION

1

S

2

8

9

CLOCK PULSE FOR

ACKNOWLEDGEMENT