References – Xilinx SP601 Hardware UG518 User Manual

Page 22

22

SP601 Hardware User Guide

UG518 (v1.1) August 19, 2009

Chapter 1: SP601 Evaluation Board

Note:

Memory U10 pin 56 address A24 is not connected on the 16 MB device. It is made available

for larger density devices.

References

See the Numonyx Flash Memory specifications for more information at

.

In addition, see the Xilinx Spartan-6 Configuration User Guide for more information at

.

L17

FLASH_CE_B

14

CE0

B3

FMC_PWR_GOOD_FLASH_RST_B

16

RP_B

X-Ref Target - Figure 1-10

NET "FLASH_A0" LOC = "K18";

NET "FLASH_A1" LOC = "K17";

NET "FLASH_A2" LOC = "J18";

NET "FLASH_A3" LOC = "J16";

NET "FLASH_A4" LOC = "G18";

NET "FLASH_A5" LOC = "G16";

NET "FLASH_A6" LOC = "H16";

NET "FLASH_A7" LOC = "H15";

NET "FLASH_A8" LOC = "H14";

NET "FLASH_A9" LOC = "H13";

NET "FLASH_A10" LOC = "F18";

NET "FLASH_A11" LOC = "F17";

NET "FLASH_A12" LOC = "K13";

NET "FLASH_A13" LOC = "K12";

NET "FLASH_A14" LOC = "E18";

NET "FLASH_A15" LOC = "E16";

NET "FLASH_A16" LOC = "G13";

NET "FLASH_A17" LOC = "H12";

NET "FLASH_A18" LOC = "D18";

NET "FLASH_A19" LOC = "D17";

NET "FLASH_A20" LOC = "G14";

NET "FLASH_A21" LOC = "F14";

NET "FLASH_A22" LOC = "C18";

NET "FLASH_A23" LOC = "C17";

NET "FLASH_A24" LOC = "F16";

NET "FPGA_D0_DIN_MISO_MISO1" LOC = "R13";

NET "FPGA_D1_MISO2" LOC = "T14";

NET "FPGA_D2_MISO3" LOC = "V14";

NET "FLASH_D3" LOC = "U5";

NET "FLASH_D4" LOC = "V5";

NET "FLASH_D5" LOC = "R3";

NET "FLASH_D6" LOC = "T3";

NET "FLASH_D7" LOC = "R5";

NET "FLASH_WE_B" LOC = "M16";

NET "FLASH_OE_B" LOC = "L18";

NET "FLASH_CE_B" LOC = "L17";

NET "FMC_PWR_GOOD_FLASH_RST_B" LOC = "B3";

Figure 1-10:

UCF Location Constraints for BPI Flash Connections

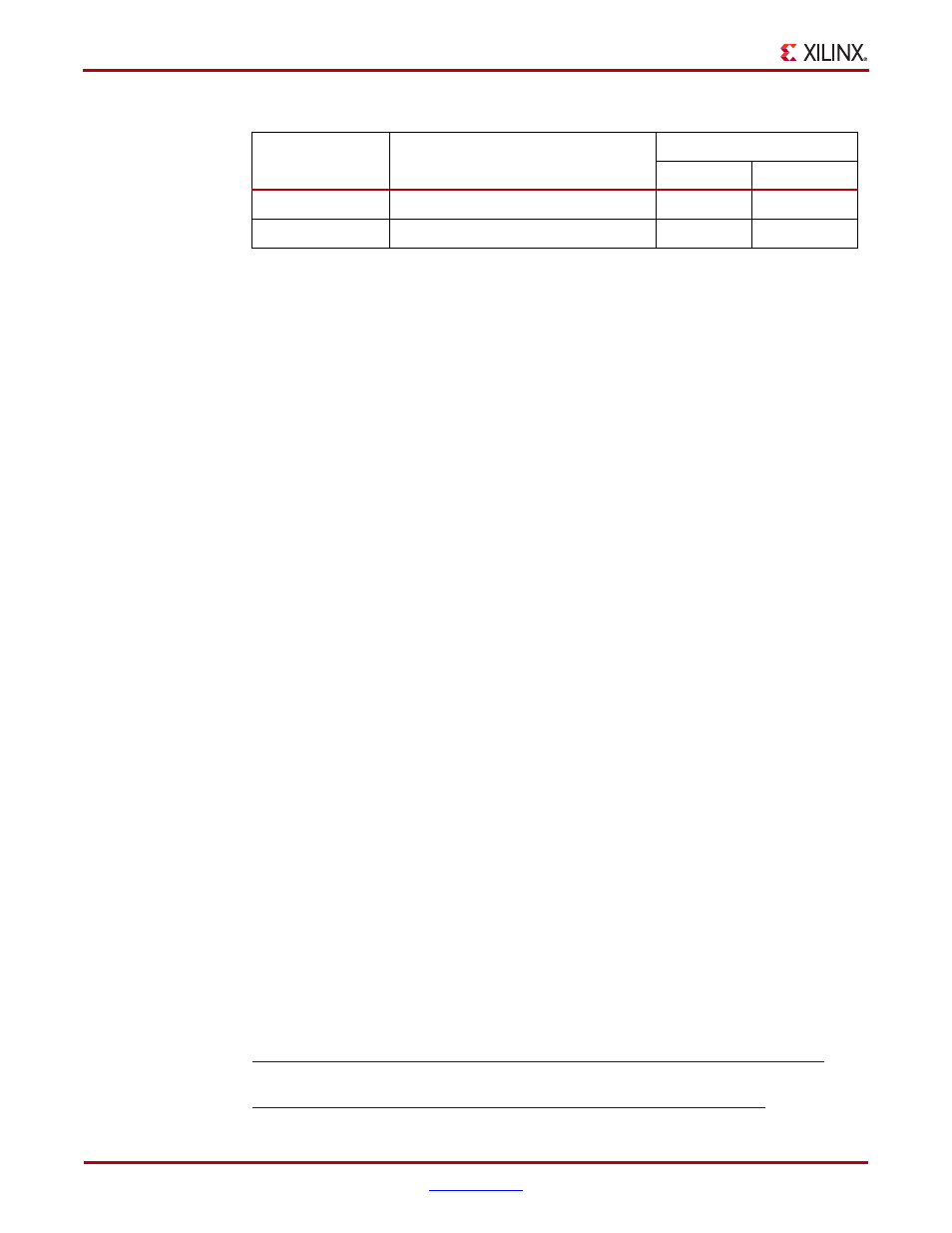

Table 1-7:

BPI Memory Connections (Cont’d)

FPGA U1 Pin

Schematic Netname

BPI Memory U10

Pin Number

Pin