Xilinx SP601 Hardware UG518 User Manual

Page 16

16

SP601 Hardware User Guide

UG518 (v1.1) August 19, 2009

Chapter 1: SP601 Evaluation Board

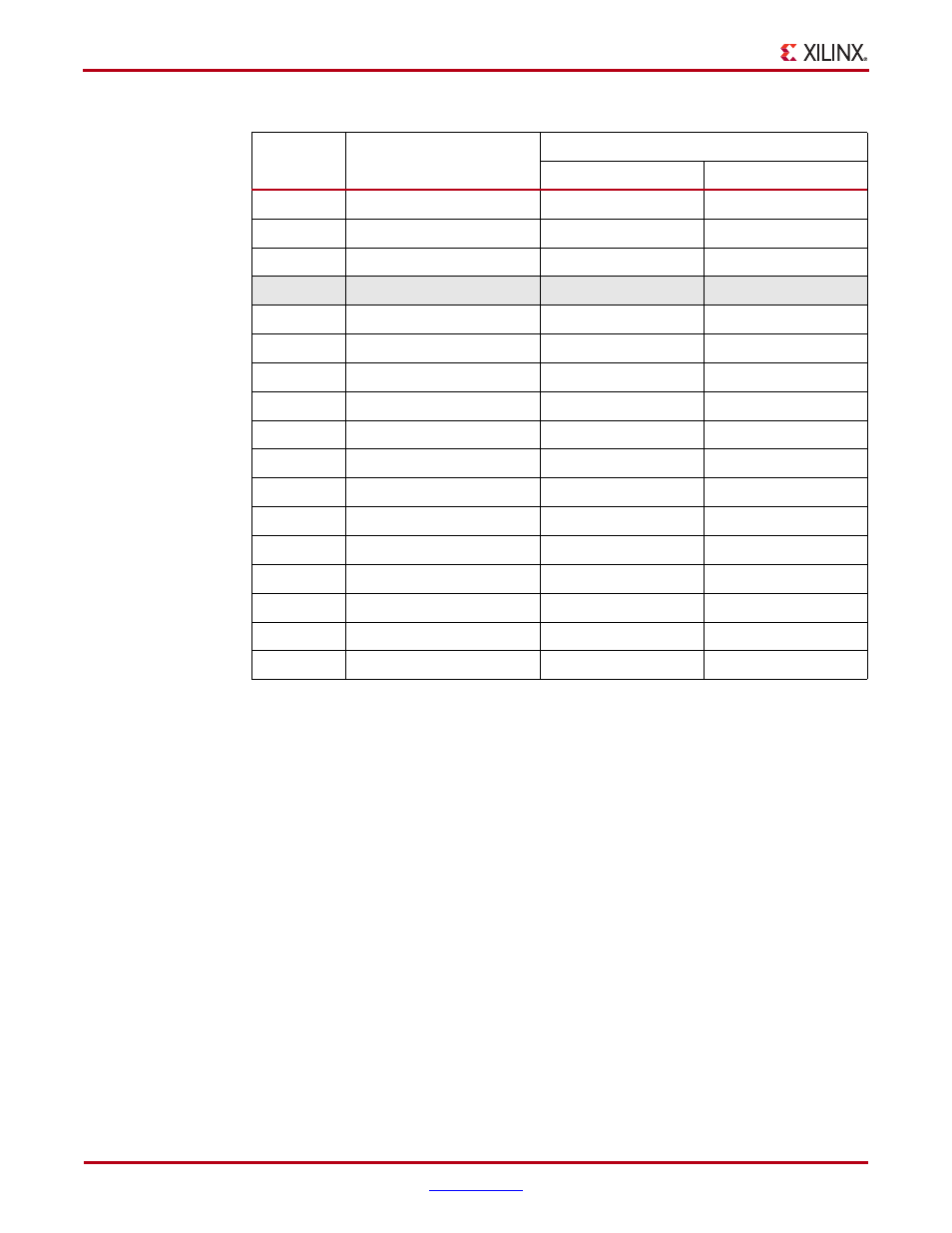

Figure 1-3

provides the user constraints file (UCF) for the DDR2 SDRAM address pins,

including the I/O pin assignment and the I/O standard used.

F2

DDR2_BA0

L2

BA0

F1

DDR2_BA1

L3

BA1

E1

DDR2_BA2

L1

BA2

E3

DDR2_WE_B

K3

WE

L5

DDR2_RAS_B

K7

RAS

K5

DDR2_CAS_B

L7

CAS

K6

DDR2_ODT

K9

ODT

G3

DDR2_CLK_P

J8

CK

G1

DDR2_CLK_N

K8

CK

H7

DDR2_CKE

K2

CKE

L4

DDR2_LDQS_P

F7

LDQS

L3

DDR2_LDQS_N

E8

LDQS

P2

DDR2_UDQS_P

B7

UDQS

P1

DDR2_UDQS_N

A8

UDQS

K3

DDR2_LDM

F3

LDM

K4

DDR2_UDM

B3

UDM

X-Ref Target - Figure 1-3

NET "DDR2_A12" LOC ="G6";| IOSTANDARD = SSTL18_II ;

NET "DDR2_A11" LOC ="D3";| IOSTANDARD = SSTL18_II ;

NET "DDR2_A10" LOC ="F4";| IOSTANDARD = SSTL18_II ;

NET "DDR2_A9" LOC ="D1"; | IOSTANDARD = SSTL18_II ;

NET "DDR2_A8" LOC ="D2"; | IOSTANDARD = SSTL18_II ;

NET "DDR2_A7" LOC ="H6"; | IOSTANDARD = SSTL18_II ;

NET "DDR2_A6" LOC ="H3"; | IOSTANDARD = SSTL18_II ;

NET "DDR2_A5" LOC ="H4"; | IOSTANDARD = SSTL18_II ;

NET "DDR2_A4" LOC ="F3"; | IOSTANDARD = SSTL18_II ;

NET "DDR2_A3" LOC ="L7"; | IOSTANDARD = SSTL18_II ;

NET "DDR2_A2" LOC ="H5"; | IOSTANDARD = SSTL18_II ;

NET "DDR2_A1" LOC ="J6"; | IOSTANDARD = SSTL18_II ;

NET "DDR2_A0" LOC ="J7"; | IOSTANDARD = SSTL18_II ;

Figure 1-3:

UCF Location Constraints for DDR2 SDRAM Address Inputs

Table 1-5:

DDR2 Component Memory Connections (Cont’d)

FPGA U1

Schematic Netname

Memory U2

Pin Number

Name