Xilinx SP601 Hardware UG518 User Manual

Page 15

SP601 Hardware User Guide

15

UG518 (v1.1) August 19, 2009

Detailed Description

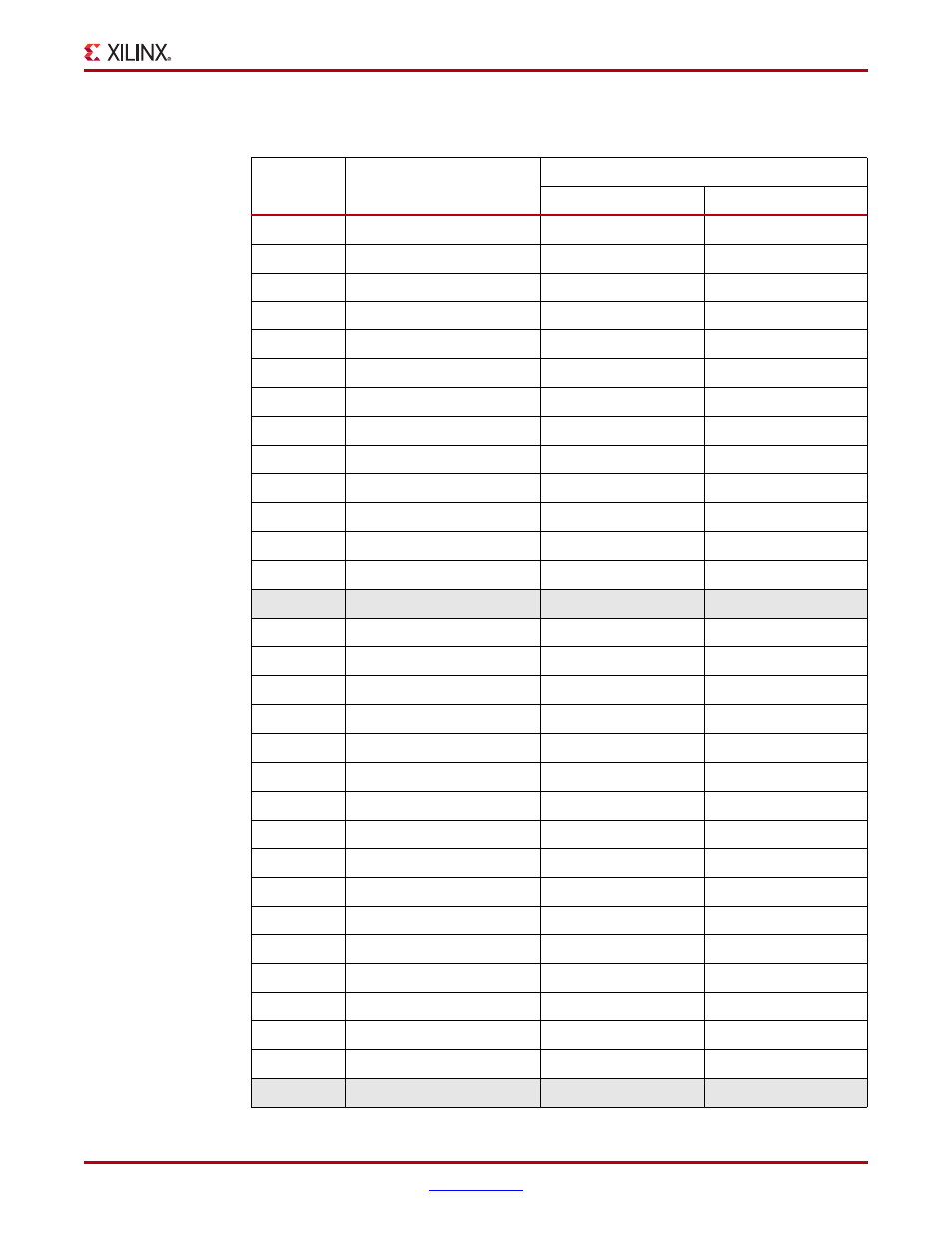

Table 1-5

shows the connections and pin numbers for the DDR2 Component Memory.

Table 1-5:

DDR2 Component Memory Connections

FPGA U1

Schematic Netname

Memory U2

Pin Number

Name

J7

DDR2_A0

M8

A0

J6

DDR2_A1

M3

A1

H5

DDR2_A2

M7

A2

L7

DDR2_A3

N2

A3

F3

DDR2_A4

N8

A4

H4

DDR2_A5

N3

A5

H3

DDR2_A6

N7

A6

H6

DDR2_A7

P2

A7

D2

DDR2_A8

P8

A8

D1

DDR2_A9

P3

A9

F4

DDR2_A10

M2

A10

D3

DDR2_A11

P7

A11

G6

DDR2_A12

R2

A12

L2

DDR2_DQ0

G8

DQ0

L1

DDR2_DQ1

G2

DQ1

K2

DDR2_DQ2

H7

DQ2

K1

DDR2_DQ3

H3

DQ3

H2

DDR2_DQ4

H1

DQ4

H1

DDR2_DQ5

H9

DQ5

J3

DDR2_DQ6

F1

DQ6

J1

DDR2_DQ7

F9

DQ7

M3

DDR2_DQ8

C8

DQ8

M1

DDR2_DQ9

C2

DQ9

N2

DDR2_DQ10

D7

DQ10

N1

DDR2_DQ11

D3

DQ11

T2

DDR2_DQ12

D1

DQ12

T1

DDR2_DQ13

D9

DQ13

U2

DDR2_DQ14

B1

DQ14

U1

DDR2_DQ15

B9

DQ15