Detailed description – Xilinx SP601 Hardware UG518 User Manual

Page 12

12

SP601 Hardware User Guide

UG518 (v1.1) August 19, 2009

Chapter 1: SP601 Evaluation Board

Detailed Description

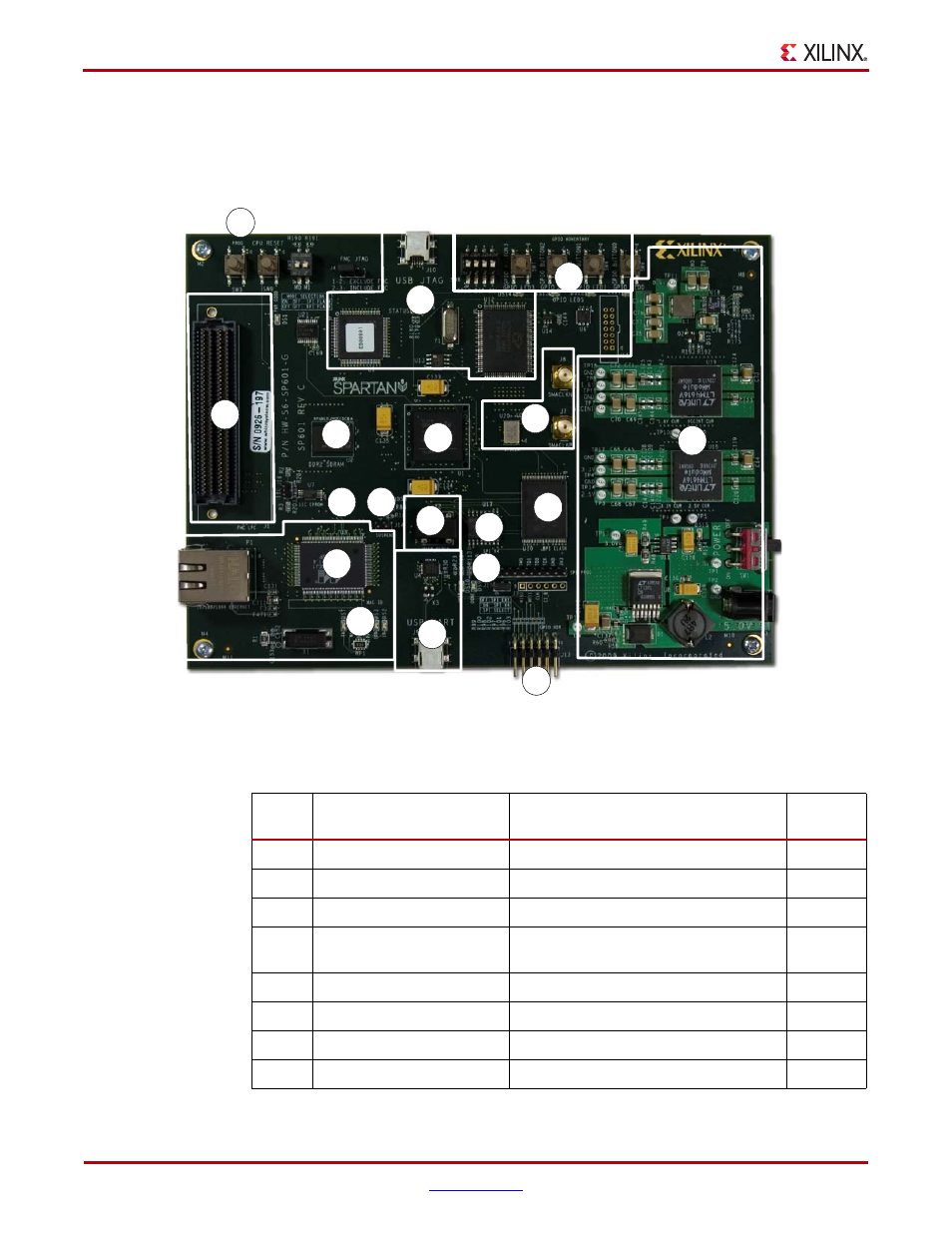

Figure 1-2

shows a board photo with numbered features corresponding to

Table 1-1

and

the section headings in this document.

The numbered features in

Figure 1-2

correlate to the features and notes listed in

Table 1-1

.

X-Ref Target - Figure 1-2

Figure 1-2:

SP601 Board Photo

11

77

22

33

44

55

66

88

99

10

10

12

12

13

13

14

14

15

15

88

16

16

11

11

13

13

Table 1-1:

SP601 Features

Number

Feature

Notes

Schematic

Page

1 Spartan-6

FPGA

XC6SLX16-2CSG324

2

DDR2 Component

Hard memory controller w/ OCT

5

3

SPI x4 Flash and Headers

SPI select and External Headers

8

4

Linear Flash BPI

StrataFlash 8-bit (J3 device), 3 pins

shared w/ SPI x4

8

5

10/100/1000 Ethernet PHY

GMII Marvell Alaska PHY

7

6

RS232 UART (USB Bridge)

Uses CP2103 Serial-to-USB connection

10

7

IIC

Goes to Header and VITA 57.1 FMC

10

8

Clock, socket, SMA

Differential, Single-Ended, Differential

9