2 peripheral reset control register (prcr) [1c05h, Section 1.7.5.2 – Texas Instruments TMS3320C5515 User Manual

Page 74

System Configuration and Control

www.ti.com

To reset a peripheral or group of peripherals, follow these steps:

1. Set COUNT = 08h in PSRCR.

2. Initiate the desired peripheral reset by setting to 1 the bits of PRCR.

3. Do not attempt to access the peripheral for at least the number of clock cycles set in the PSRCR

register. A repeated NOP may be necessary.

In some cases, a single reset is used for multiple peripherals. For example, PG4_RST controls the reset

to the LCD controller, I2S2, I2S3, UART, and SPI.

1.7.5.1

Peripheral Software Reset Counter Register (PSRCR) [1C04h]

The Peripheral Software Reset Counter Register (PSRCR) is shown in

and described in

Figure 1-46. Peripheral Software Reset Counter Register (PSRCR) [1C04h]

15

0

COUNT

R/W-0

LEGEND: R/W = Read/Write; -n = value after reset

Table 1-58. Peripheral Software Reset Counter Register (PSRCR) Field Descriptions

Bit

Field

Value

Description

15-0

COUNT

0-FFFFh

Count bits. These bits specify the number of system clock (SYSCLK) cycles the software

reset signals are asserted. When the software counter reaches 0, the software reset bits

will be cleared to 0. Always initialize this field with a value of at least 08h.

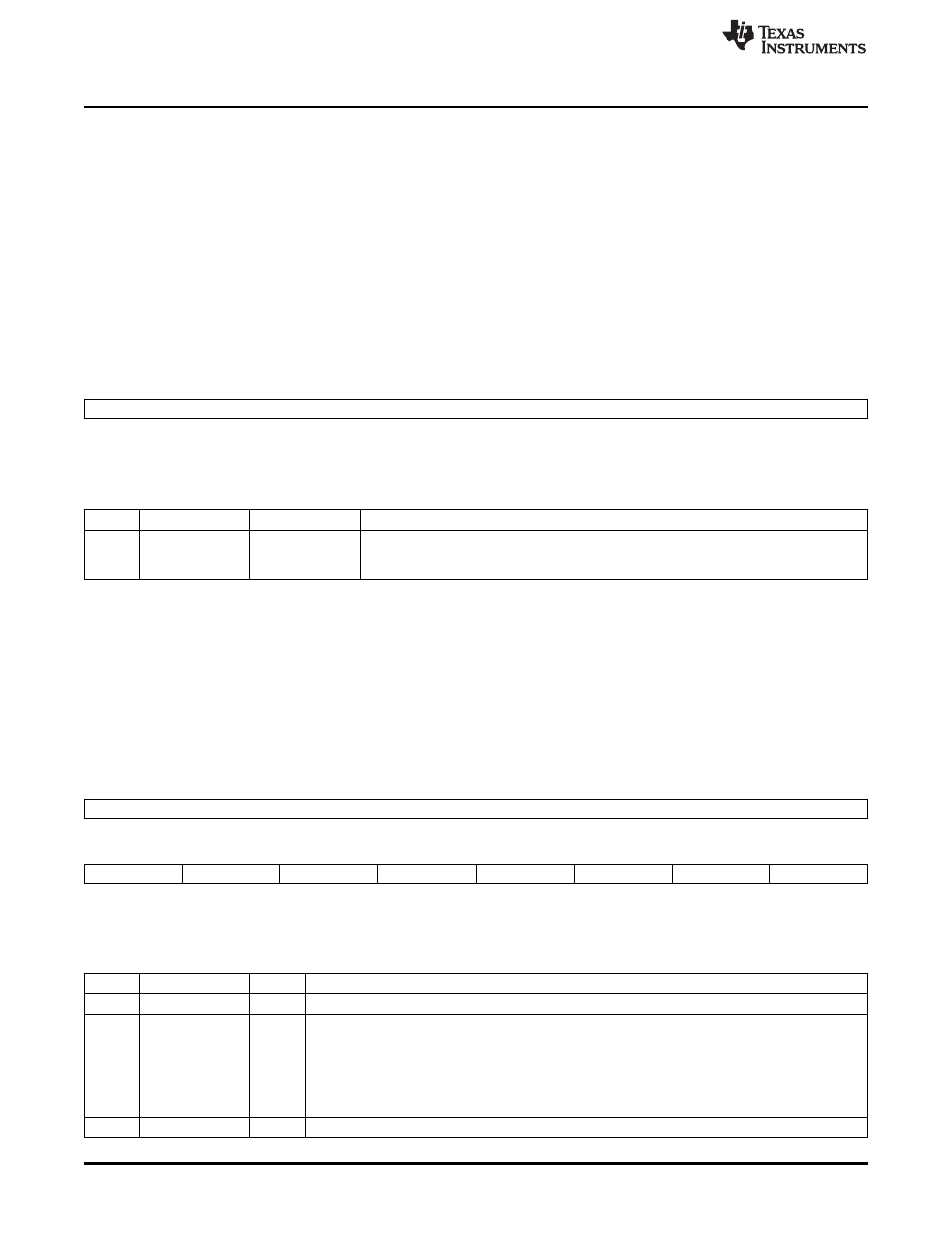

1.7.5.2

Peripheral Reset Control Register (PRCR) [1C05h]

Writing a 1 to any bits in this register initiates the reset sequence for the associated peripherals. The

associated peripherals will be held in reset for the duration of clock cycles set in the PSRCR register and

they should not be accessed during that time. Reads of this register return the state of the reset signal for

the associated peripherals. In other words, polling may be used to wait for the reset to become

de-asserted.

The Peripheral Reset Control Register (PRCR) is shown in

and described in

Figure 1-47. Peripheral Reset Control Register (PRCR) [1C05h]

15

14

13

12

11

10

9

8

Reserved

R-0

7

6

5

4

3

2

1

0

PG4_RST

Reserved

PG3_RST

DMA_RST

USB_RST

SAR_RST

PG1_RST

I2C_RST

R/W-0

R-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 1-59. Peripheral Reset Control Register (PRCR) Field Descriptions

Bit

Field

Value

Description

15-8

Reserved

0

Reserved. Always write 0 to these bits.

7

PG4_RST

Peripheral group 4 software reset bit. Drives the LCD, I2S2, I2S3, UART, and SPI reset signal.

Write 0

Writing zero has no effect

Write 1

Writing one starts resetting the peripheral group

Read 0

Reading zero means that peripheral group is out of reset

Read 1

Reading one means the peripheral group is being held in reset and should not be accessed

6

Reserved

0

Reserved, always write 0 to this bit.

74

System Control

SPRUFX5A – October 2010 – Revised November 2010

Copyright © 2010, Texas Instruments Incorporated