1 dma synchronization events, 2 dma configuration registers – Texas Instruments TMS3320C5515 User Manual

Page 71

www.ti.com

System Configuration and Control

1.7.4.1

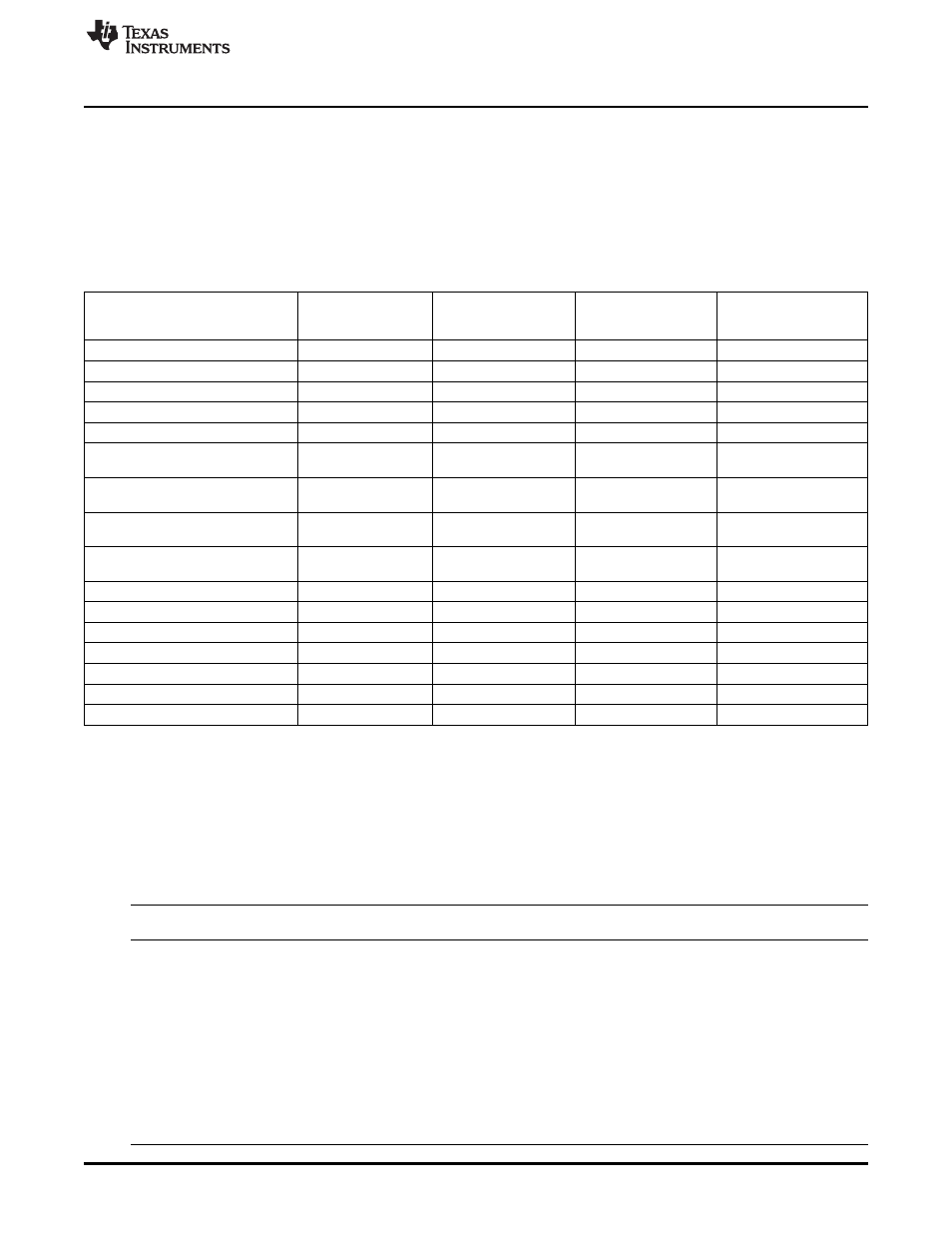

DMA Synchronization Events

The DMA controllers allow activity in their channels to be synchronized to selected events. The DSP

supports 20 separate synchronization events and each channel can be tied to separate sync events

independent of the other channels. Synchronization events are selected by programming the CHnEVT

field in the DMAn channel event source registers (DMAnCESR1 and DMAnCESR2) (where n is an

integer, 0-3, representing each of the 4 DMAs). The synchronization events available to each DMA

controller are shown in

.

Table 1-52. Channel Synchronization Events for DMA Controllers

DMA0

DMA1

DMA2

DMA3 Synchronization

Synchronization

Synchronization

Synchronization

Event

CHmEVT Options

Event

Event

Event

0000b

Reserved

Reserved

Reserved

Reserved

0001b

I2S0 transmit event

I2S2 transmit event

I2C transmit event

I2S1 transit event

0010b

I2S0 receive event

I2S2 receive event

I2C receive event

I2S1 receive event

0011b

Reserved

Reserved

SAR A/D event

Reserved

0100b

Reserved

Reserved

I2S3 transmit event

Reserved

MMC/SD0 transmit

0101b

event

UART transmit event

I2S3 receive event

Reserved

0110b

MMC/SD0 receive

event

UART receive event

Reserved

Reserved

0111b

MMC/SD1 transmit

event

Reserved

Reserved

Reserved

1000b

MMC/SD1 receive

event

Reserved

Reserved

Reserved

1001b

Reserved

Reserved

Reserved

Reserved

1010v

Reserved

Reserved

Reserved

Reserved

1011b

Reserved

Reserved

Reserved

Reserved

1100b

Timer 0 event

Timer 0 event

Timer 0 event

Timer 0 event

1101b

Timer 1 event

Timer 1 event

Timer 1 event

Timer 1 event

1110b

Timer 2 event

Timer 2 event

Timer 2 event

Timer 2 event

1111b

Reserved

Reserved

Reserved

Reserved

1.7.4.2

DMA Configuration Registers

The system-level DMA registers are listed in

. The DMA interrupt flag and enable registers

(DMAIFR and DMAIER) are used to control the aggregation and CPU interrupt generation for the four

DMA controllers and their associated channels. In addition, there are two registers per DMA controller

which control event synchronization in each channel; the DMAn channel event source registers

(DMAnCESR1 and DMAnCESR2).

Table 1-53. System Registers Related to the DMA Controllers

CPU Word

Acronym

Register Description

Address

1C30h

DMAIFR

DMA Interrupt Flag Register

1C31h

DMAIER

DMA Interrupt Enable Register

1C1Ah

DMA0CESR1

DMA0 Channel Event Source Register 1

1C1Bh

DMA0CESR2

DMA0 Channel Event Source Register 2

1C1Ch

DMA1CESR1

DMA1 Channel Event Source Register 1

1C1Dh

DMA1CESR2

DMA1 Channel Event Source Register 2

1C36h

DMA2CESR1

DMA2 Channel Event Source Register 1

1C37h

DMA2CESR2

DMA2 Channel Event Source Register 2

1C38h

DMA3CESR1

DMA3 Channel Event Source Register 1

1C39h

DMA3CESR2

DMA3 Channel Event Source Register 2

71

SPRUFX5A – October 2010 – Revised November 2010

System Control

Copyright © 2010, Texas Instruments Incorporated