5 clock configuration register 1 (ccr1) [1c1eh, 6 clock configuration register 2 (ccr2) [1c1fh, Section 1.4.4.5 – Texas Instruments TMS3320C5515 User Manual

Page 32: Section 1.4.4.6

System Clock Generator

www.ti.com

1.4.4.5

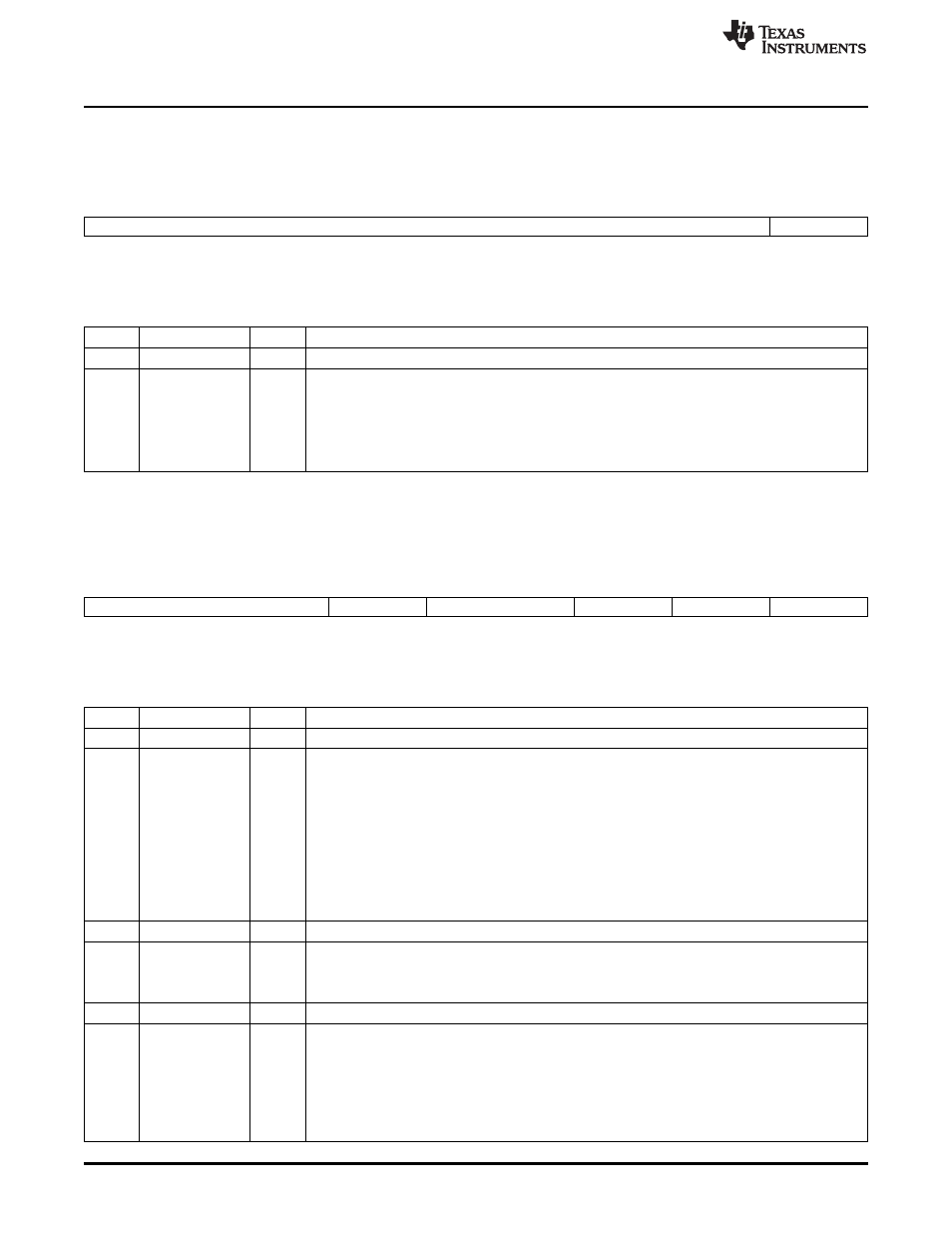

Clock Configuration Register 1 (CCR1) [1C1Eh]

The clock configuration register 1 (CCR1) is shown in

and described in

Figure 1-10. Clock Configuration Register 1 (CCR1) [1C1Eh]

15

1

0

Reserved

SDCLK_EN

R-0

R/W-0

LEGEND: R = Read only; -n = value after reset

Table 1-17. Clock Configuration Register 1 (CCR1) Field Descriptions

Bit

Field

Value

Description

15-1

Reserved

0

Reserved. This bit must be kept as 0 during writes to this register.

0

SDCLK_EN

SDRAM clock enable control. When ON, the EM_SDCLK pin will drive the clock signal at the

SYSCLK frequency if in full_rate mode or at SYSCLK frequency divided by 2 if in half_rate mode.

When OFF, the EM_SDCLK pin will drive low. Transitions from ON to OFF and OFF to ON are not

guaranteed to be glitchless. Therefore, the EMIF should be reset after any change.

0

EM_SDCLK off (default)

1

EM_SDCLK on. This bit must be set to 1 before using SDRAM or mSDRAM.

1.4.4.6

Clock Configuration Register 2 (CCR2) [1C1Fh]

The clock configuration register 2 (CCR2) is shown in

and described in

Figure 1-11. Clock Configuration Register 2 (CCR2) [1C1Fh]

15

6

5

4

3

2

1

0

Reserved

SYSCLKSRC

Reserved

CLKSELSTAT

Reserved

SYSCLKSEL

R-0

R-0

R/W-0

R-0

R-0

R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 1-18. Clock Configuration Register 2 (CCR2) Field Descriptions

Bit

Field

Value

Description

15-6

Reserved

0

Reserved.

5-4

SYSCLKSRC

System clock source status bits. These read-only bits reflect the source for the system clock. This

status register exists to indicate that switching from the PLL BYPASS_MODE to the PLL_MODE

was successful or not. Logic exists on the chip to prevent switching to PLL_MODE if the PLL has its

PWRDN bit already asserted. However, this circuit does not protect against asserting the PWRDN

bit after already in PLL_MODE. Therefore, software must ultimately make sure not to do something

that would cause the system clock to be lost.

0

The system clock generator is in bypass mode; SYSCLK is driven by the RTC oscillator output.

1h

The system clock generator is in PLL mode; the RTC oscillator output provides the input clock.

2h

The system clock generator is in bypass mode; SYSCLK is driven by CLKIN.

3h

The system clock generator is in PLL mode; the CLKIN pin provides the input clock.

3

Reserved

0

Reserved. This bit must be written to be 0.

2

CLKSELSTAT

CLK_SEL pin status bit. This reflects the state of the CLK_SEL pin.

0

CLK_SEL pin is low (RTC input clock selected).

1

CLK_SEL pin is high (CLKIN input clock selected).

1

Reserved

0

Reserved. This bit must be written to be 0.

0

SYSCLKSEL

System clock source select bit. This bit is used to select between the two main clocking modes for

the DSP: bypass and PLL mode. In bypass mode, the DSP clock generator is bypassed and the

system clock is set to either CLKIN or the RTC output (as determined by the CLKSEL pin). In PLL

mode, the system clock is set to the output of the DSP clock generator. Logic in the system clock

generator prevents switching from bypass mode to PLL mode if the PLL is powered down.

0

Bypass mode is selected.

1

PLL mode is selected.

32

System Control

SPRUFX5A – October 2010 – Revised November 2010

Copyright © 2010, Texas Instruments Incorporated