3 clock configuration process, 3 clock generator domain clock gating, 4 usb domain clock gating – Texas Instruments TMS3320C5515 User Manual

Page 43: Section 1.5.3.2.3

www.ti.com

Power Management

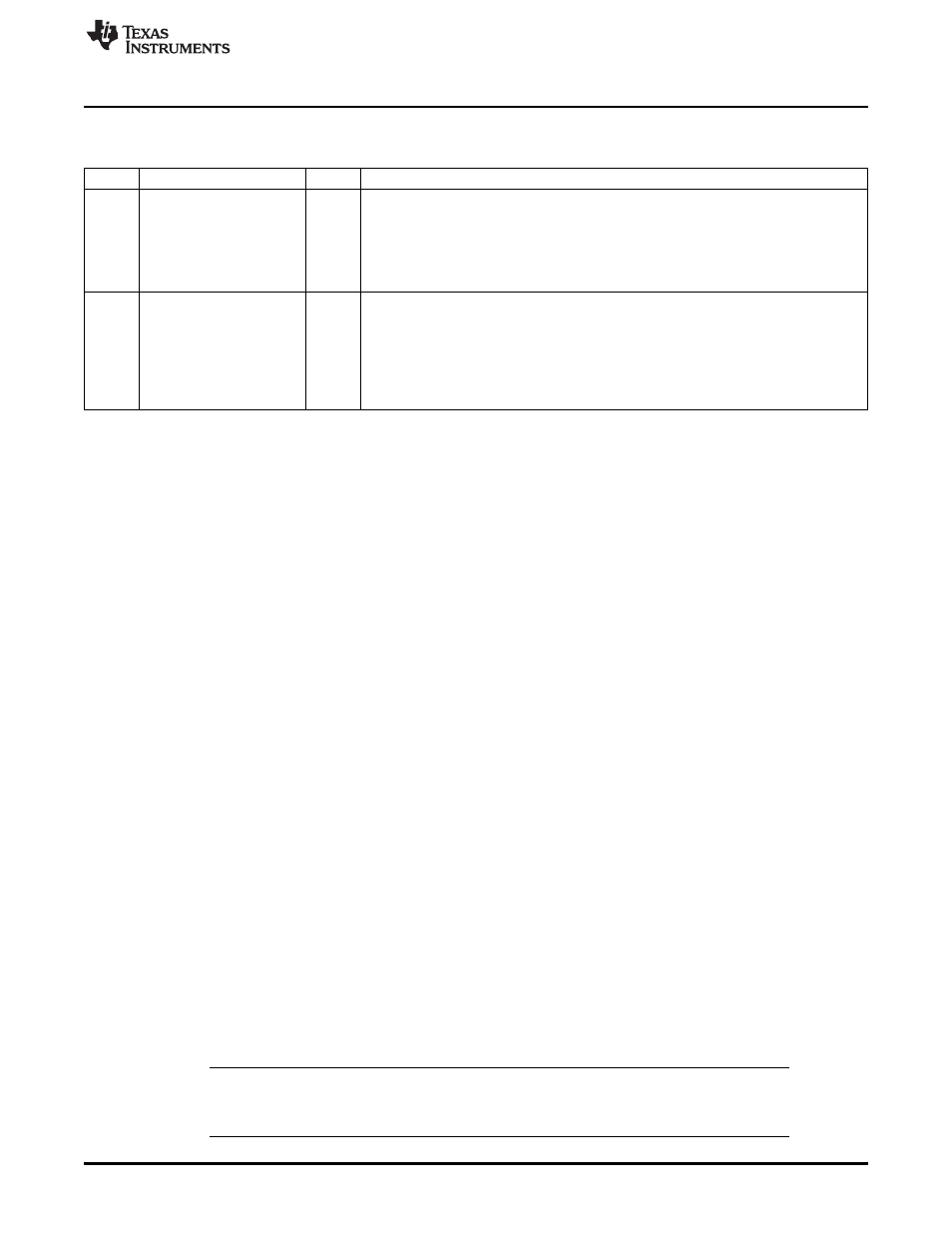

Table 1-26. Peripheral Clock Stop Request/Acknowledge Register (CLKSTOP) Field Descriptions

(continued)

Bit

Field

Value

Description

1

EMFCLKSTPACK

EMIF clock stop acknowledge bit. This bit is set to 1 when the EMIF has acknowledged a

request for its clock to be stopped. The EMIF clock should not be stopped until this bit is

set to 1.

0

The request to stop the peripheral clock has not been acknowledged.

1

The request to stop the peripheral clock has been acknowledged, the clock can be

stopped.

0

EMFCLKSTPREQ

EMIF peripheral clock stop request bit. When disabling the EMIF internal peripheral clock,

you must set this bit to 1 to request permission to stop the clock. After the EMIF

acknowledges the request (EMFCLKSTPACK = 1) you can stop the clock through the

peripheral clock gating control register 1 (PCGCR1). When enabling the EMIF internal

clock, enable the clock through PCGCR1, then set EMFCKLSTPREQ to 0.

0

Normal operating mode.

1

Request permission to stop the peripheral clock.

1.5.3.2.3 Clock Configuration Process

The clock configuration indicates which portions of the peripheral clock domain will be idle, and which will

be active. The basic steps to the clock configuration process are:

1. Wait for completion of all DMA transfers. You can poll the DMA transfer status and disable DMA

transfers through the DMA registers.

2. If idling the EMIF, USB, and UART clock, set the corresponding clock stop request bit in CLKSTOP.

3. Wait for confirmation from the module that its clock can be stopped by polling the clock stop

acknowledge bits of CLKSTOP.

4. Set the clock configuration for the peripheral domain through PCGCR1 and PCGCR2. The clock

configuration takes place as soon as you write to these registers; the idle instruction is not required

1.5.3.3

Clock Generator Domain Clock Gating

To save power, the system clock generator can be placed in its BYPASS MODE and its PLL can be

placed in power down mode. When the system clock generator is in the BYPASS MODE, the clock

generator is not used and the system clock (SYSCLK) is driven by either the CLKIN pin or the real-time

clock (RTC). For more information entering and exiting the bypass mode of the clock generator, see

.

When the clock generator is placed in its bypass mode, the PLL continues to generate a clock output. You

can save additional power by powering down the PLL.

provides more information on

powering down the PLL.

1.5.3.4

USB Domain Clock Gating

The USB peripheral has two clock domains. The first is a high speed domain that has its clock supplied by

a dedicated USB PLL. The reference clock for the USB PLL is the 12.0 MHz USB oscillator. The clock

output from the PLL must support the serial data stream that, in high-speed mode, is at a rate of 480

Mb/s. The second clock into the USB peripheral handles the data once it has been packetized and

transported in parallel fashion. This clock supports all of the USB registers, CDMA, FIFO, etc., and is

clocked by SYSCLK. In order to keep up with the serial data stream, the USB requires SYSCLK to be at

least 30 MHz for low-speed/full-speed modes and at least 60 MHz for high-speed mode.

By stopping both of these clocks, it is possible to reduce the USB's active power consumption (in the

digital logic) to zero.

NOTE:

Stopping clocks to a peripheral only affects active power consumption; it does not affect

leakage power consumption. USB leakage power consumption can be reduced to zero by

not powering the USB.

43

SPRUFX5A – October 2010 – Revised November 2010

System Control

Copyright © 2010, Texas Instruments Incorporated