Hpi8 timing (continued) – Texas Instruments TMS320VC5402 User Manual

Page 63

TMS320VC5402

FIXEDĆPOINT DIGITAL SIGNAL PROCESSOR

SPRS079E – OCTOBER 1998 – REVISED AUGUST 2000

63

POST OFFICE BOX 1443

•

HOUSTON, TEXAS 77251–1443

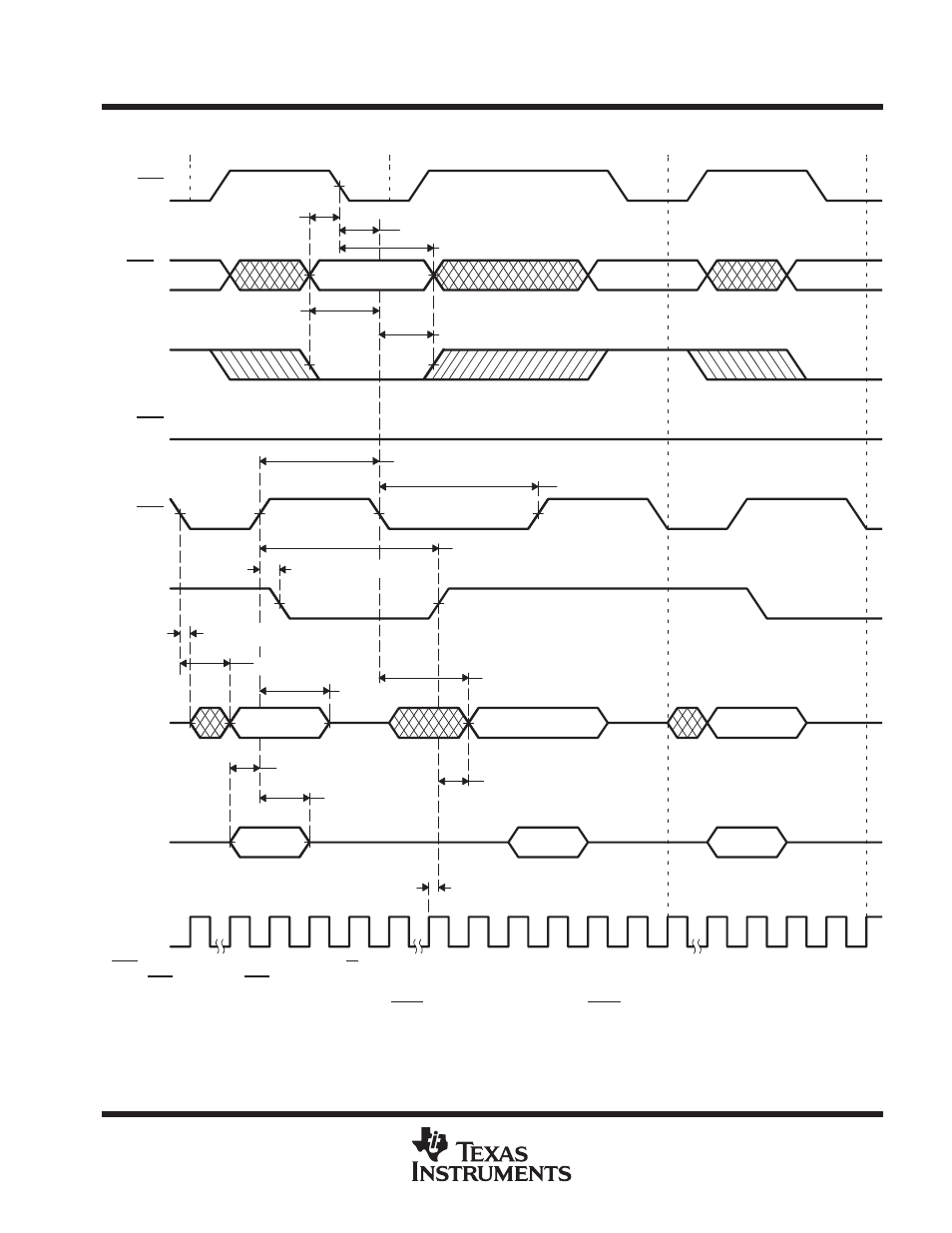

HPI8 timing (continued)

Valid

tsu(HSL-DSL)

Valid

tsu(HBV-DSL)

tsu(HBV-DSL)‡

HAS

HBIL

th(DSL-HBV)

th(DSL-HBV)‡

td(DSH-HYH)

tw(DSL)

td(DSL-HDV1)

tv(HYH-HDV)

Valid

Valid

Valid

td(COH-HYH)

Valid

tw(DSH)

td(DSH-HYL)

th(DSH-HDV)R

th(DSH-HDV)W

Valid

tsu(HDV-DSH)

td(DSL-HDV2)

ten(DSL-HD)

HCS

HDS

HRDY

HD READ

Valid

HD WRITE

CLKOUT

Second Byte

First Byte

Second Byte

HAD†

† HAD refers to HCNTL0, HCNTL1, and HR/W.

‡ When HAS is not used (HAS always high)

Figure 35. Using HDS to Control Accesses (HCS Always Low)