Texas Instruments TMS320VC5402 User Manual

Page 45

TMS320VC5402

FIXEDĆPOINT DIGITAL SIGNAL PROCESSOR

SPRS079E – OCTOBER 1998 – REVISED AUGUST 2000

45

POST OFFICE BOX 1443

•

HOUSTON, TEXAS 77251–1443

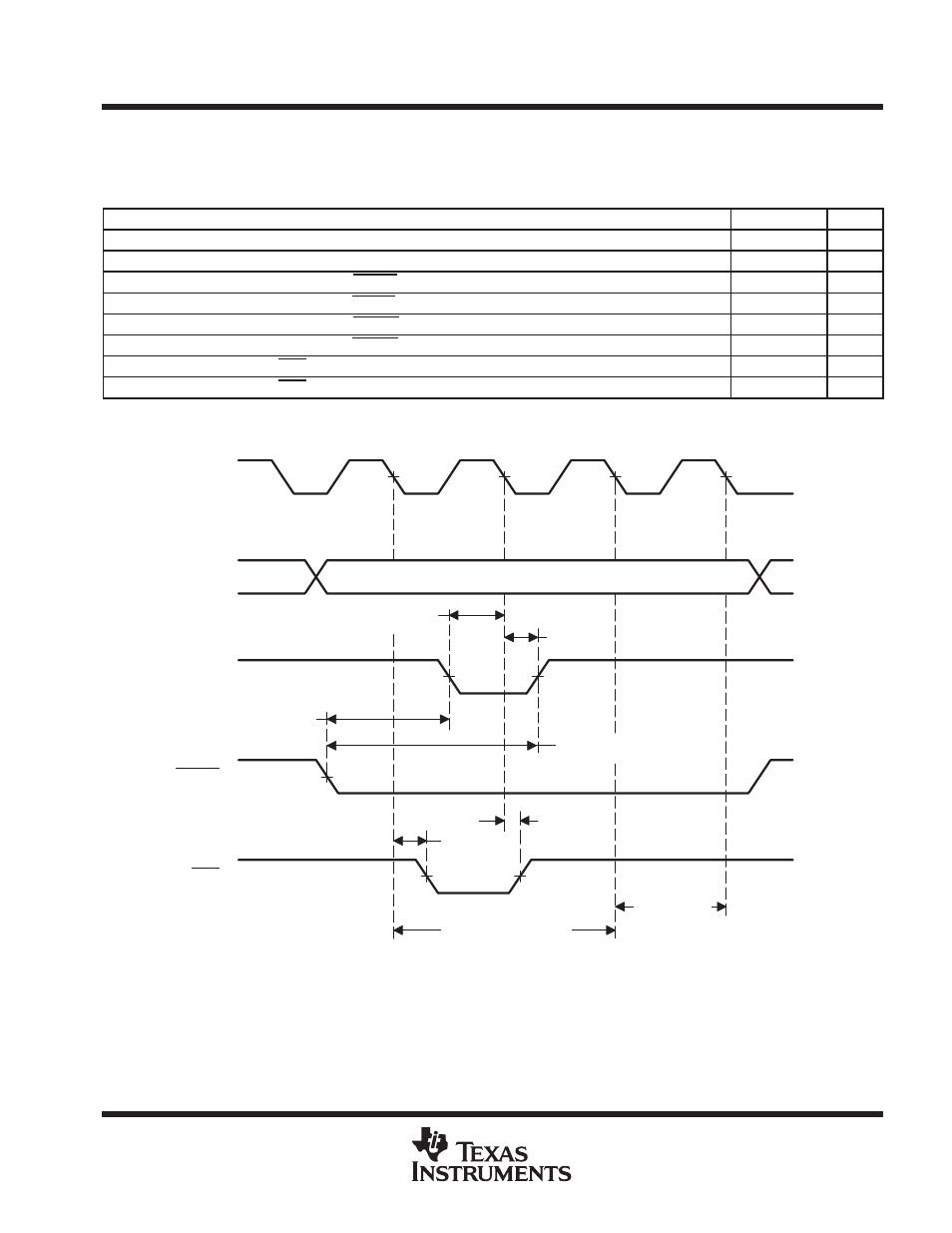

ready timing for externally generated wait states

timing requirements for externally generated wait states [H = 0.5 t

c(CO)

]

†

(see Figure 17, Figure 18,

Figure 19, and Figure 20)

MIN

MAX

UNIT

tsu(RDY)

Setup time, READY before CLKOUT low

6

ns

th(RDY)

Hold time, READY after CLKOUT low

0

ns

tv(RDY)MSTRB

Valid time, READY after MSTRB low‡

4H–8

ns

th(RDY)MSTRB

Hold time, READY after MSTRB low‡

4H

ns

tv(RDY)IOSTRB

Valid time, READY after IOSTRB low‡

5H–8

ns

th(RDY)IOSTRB

Hold time, READY after IOSTRB low‡

5H

ns

tv(MSCL)

Valid time, MSC low after CLKOUT low

–1

3

ns

tv(MSCH)

Valid time, MSC high after CLKOUT low

–1

3

ns

† The hardware wait states can be used only in conjunction with the software wait states to extend the bus cycles. To generate wait states using

READY, at least two software wait states must be programmed.

‡ These timings are included for reference only. The critical timings for READY are those referenced to CLKOUT.

MSC

MSTRB

READY

A[19:0]

CLKOUT

tv(MSCH)

tv(MSCL)

th(RDY)

th(RDY)MSTRB

tv(RDY)MSTRB

Wait State

Generated

by READY

Wait States

Generated Internally

tsu(RDY)

NOTE A: A[19:16] are always driven low during accesses to external data space.

Figure 17. Memory Read With Externally Generated Wait States