Hpi8 timing (continued) timing requirements – Texas Instruments TMS320VC5402 User Manual

Page 62

TMS320VC5402

FIXEDĆPOINT DIGITAL SIGNAL PROCESSOR

SPRS079E – OCTOBER 1998 – REVISED AUGUST 2000

62

POST OFFICE BOX 1443

•

HOUSTON, TEXAS 77251–1443

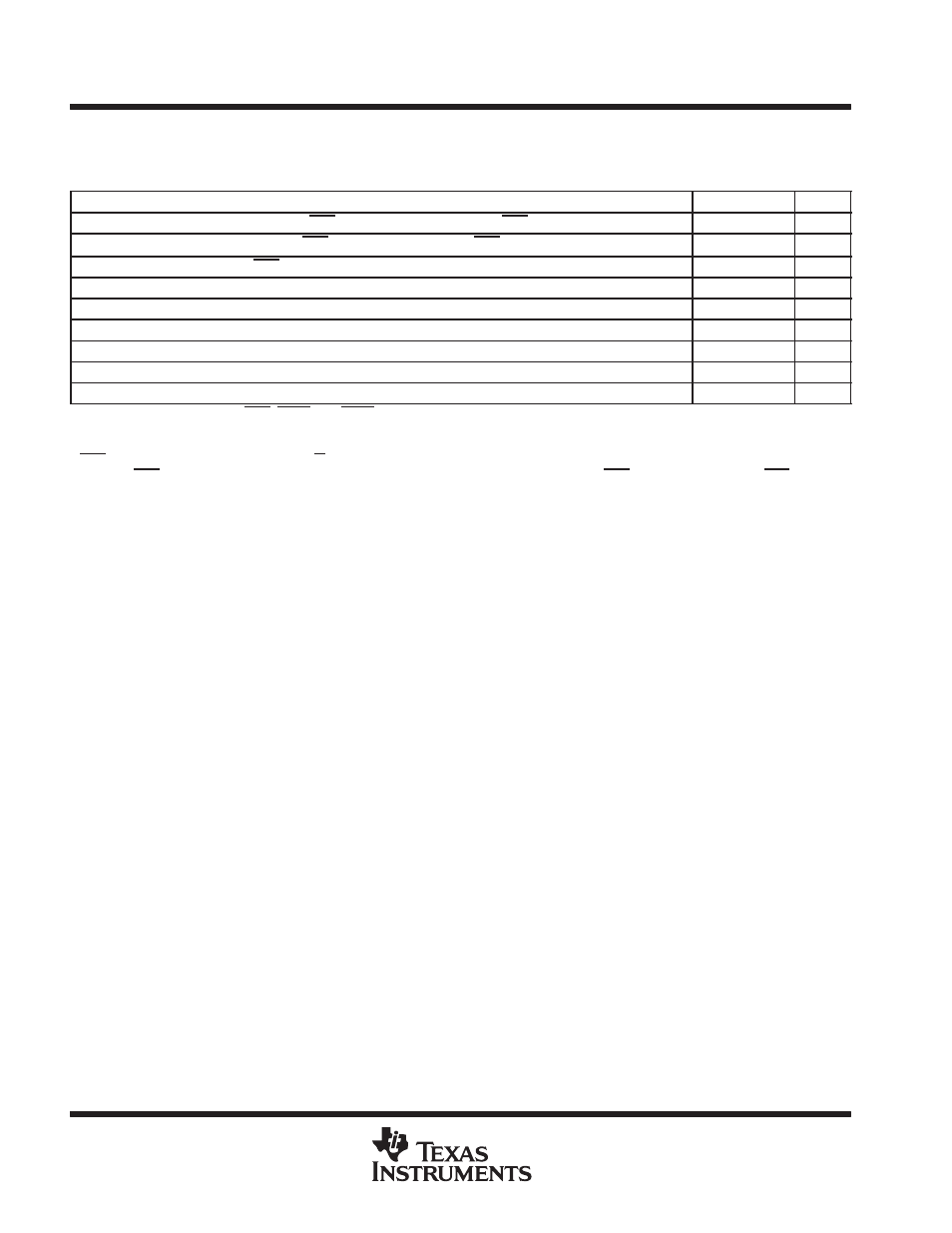

HPI8 timing (continued)

timing requirements

†‡§

(see Figure 35, Figure 36, Figure 37, and Figure 38)

MIN

MAX

UNIT

tsu(HBV-DSL)

Setup time, HBIL and HAD valid before DS low or before HAS low¶#

5

ns

th(DSL-HBV)

Hold time, HBIL and HAD valid after DS low or after HAS low¶#

5

ns

tsu(HSL-DSL)

Setup time, HAS low before DS low

10

ns

tw(DSL)

Pulse duration, DS low

20

ns

tw(DSH)

Pulse duration, DS high

10

ns

tsu(HDV-DSH)

Setup time, HDx valid before DS high, HPI write

2

ns

th(DSH-HDV)W

Hold time, HDx valid after DS high, HPI write

3

ns

tsu(GPIO-COH)

Setup time, HDx input valid before CLKOUT high, HDx configured as general-purpose input

6

ns

th(GPIO-COH)

Hold time, HDx input valid after CLKOUT high, HDx configured as general-purpose input

0

ns

† DS refers to the logical OR of HCS, HDS1, and HDS2.

‡ HDx refers to any of the HPI data bus pins (HD0, HD1, HD2, etc.).

§ GPIO refers to the HD pins when they are configured as general-purpose input/outputs.

¶ HAD refers to HCNTL0, HCNTL1, and H/RW.

# When the HAS signal is used to latch the control signals, this timing refers to the falling edge of the HAS signal. Otherwise, when HAS is not used

(always high), this timing refers to the falling edge of DS.