Divide-by-two clock option (pll disabled), Timing requirements (see figure 11) – Texas Instruments TMS320VC5402 User Manual

Page 37

TMS320VC5402

FIXEDĆPOINT DIGITAL SIGNAL PROCESSOR

SPRS079E – OCTOBER 1998 – REVISED AUGUST 2000

37

POST OFFICE BOX 1443

•

HOUSTON, TEXAS 77251–1443

divide-by-two clock option (PLL disabled)

The frequency of the reference clock provided at the X2/CLKIN pin can be divided by a factor of two to generate

the internal machine cycle. The selection of the clock mode is described in the clock generator section.

When an external clock source is used, the frequency injected must conform to specifications listed in the timing

requirements table.

NOTE:

All revisions of the ’5402 can be operated with an external clock source, provided that the proper

voltage levels be driven on the X2/CLKIN pin. It should be noted that the X2/CLKIN pin is referenced to

the device 1.8V power supply (CVdd), rather than the 3V I/O supply (DVdd). Refer to the recommended

operating conditions section of this document for the allowable voltage levels of the X2/CLKIN pin.

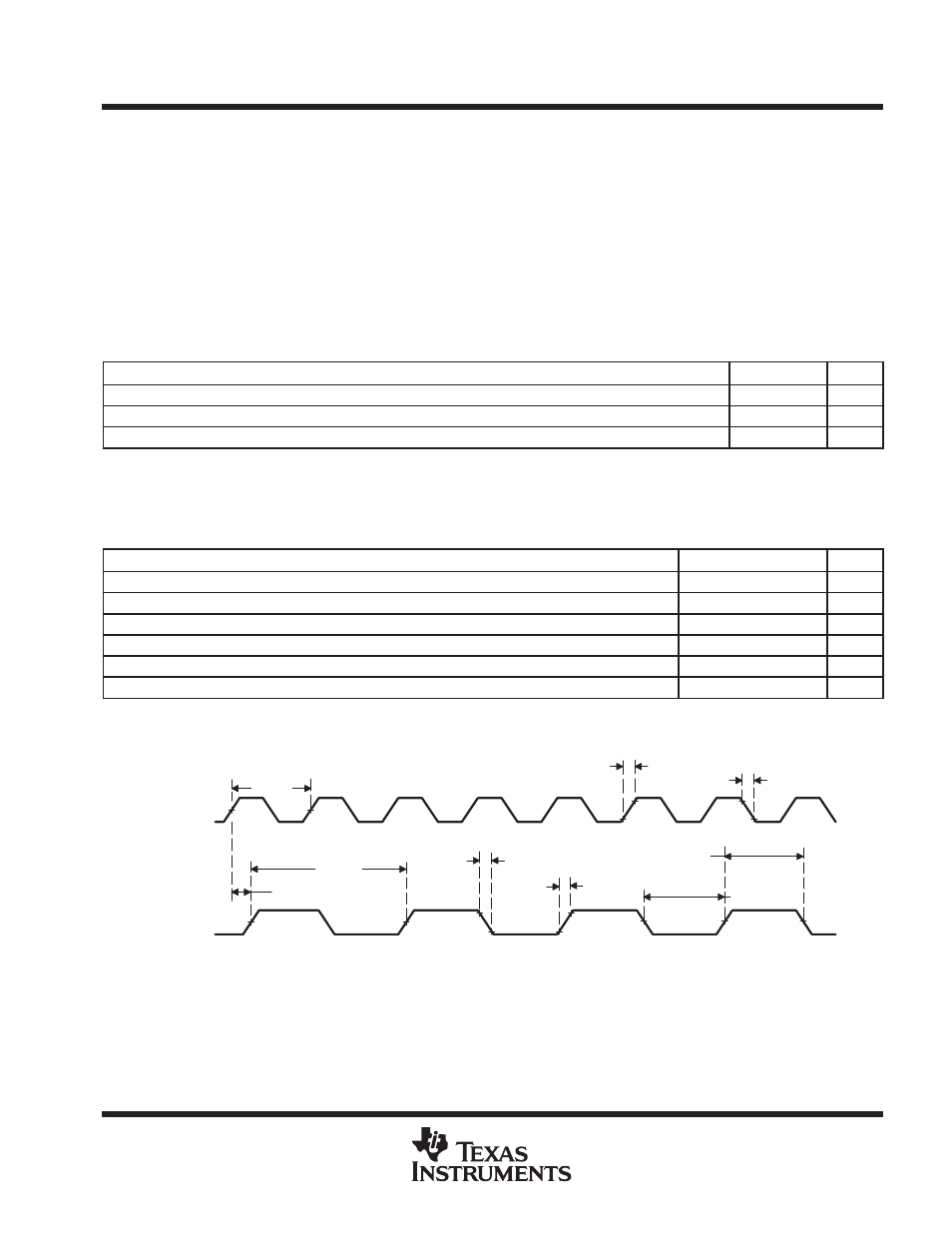

timing requirements (see Figure 11)

MIN

MAX

UNIT

tc(CI)

Cycle time, X2/CLKIN

20

†

ns

tf(CI)

Fall time, X2/CLKIN

8

ns

tr(CI)

Rise time, X2/CLKIN

8

ns

† This device utilizes a fully static design and therefore can operate with tc(CI) approaching

∞

. The device is characterized at frequencies

approaching 0 Hz.

switching characteristics over recommended operating conditions [H = 0.5t

c(CO)

]

†

(see Figure 10,

Figure 11, and the recommended operating conditions table)

PARAMETER

MIN

TYP

MAX

UNIT

tc(CO)

Cycle time, CLKOUT

10‡

2tc(CI)

†

ns

td(CIH-CO)

Delay time, X2/CLKIN high to CLKOUT high/low

4

10

17

ns

tf(CO)

Fall time, CLKOUT

2

ns

tr(CO)

Rise time, CLKOUT

2

ns

tw(COL)

Pulse duration, CLKOUT low

H–2

H

ns

tw(COH)

Pulse duration, CLKOUT high

H–2

H

ns

† This device utilizes a fully static design and therefore can operate with tc(CI) approaching

∞

. The device is characterized at frequencies

approaching 0 Hz.

‡ It is recommended that the PLL clocking option be used for maximum frequency operation.

tr(CO)

tf(CO)

CLKOUT

X2/CLKIN

tw(COL)

td(CIH-CO)

tf(CI)

tr(CI)

tc(CO)

tc(CI)

tw(COH)

Figure 11. External Divide-by-Two Clock Timing