Texas Instruments TMS320VC5402 User Manual

Page 55

TMS320VC5402

FIXEDĆPOINT DIGITAL SIGNAL PROCESSOR

SPRS079E – OCTOBER 1998 – REVISED AUGUST 2000

55

POST OFFICE BOX 1443

•

HOUSTON, TEXAS 77251–1443

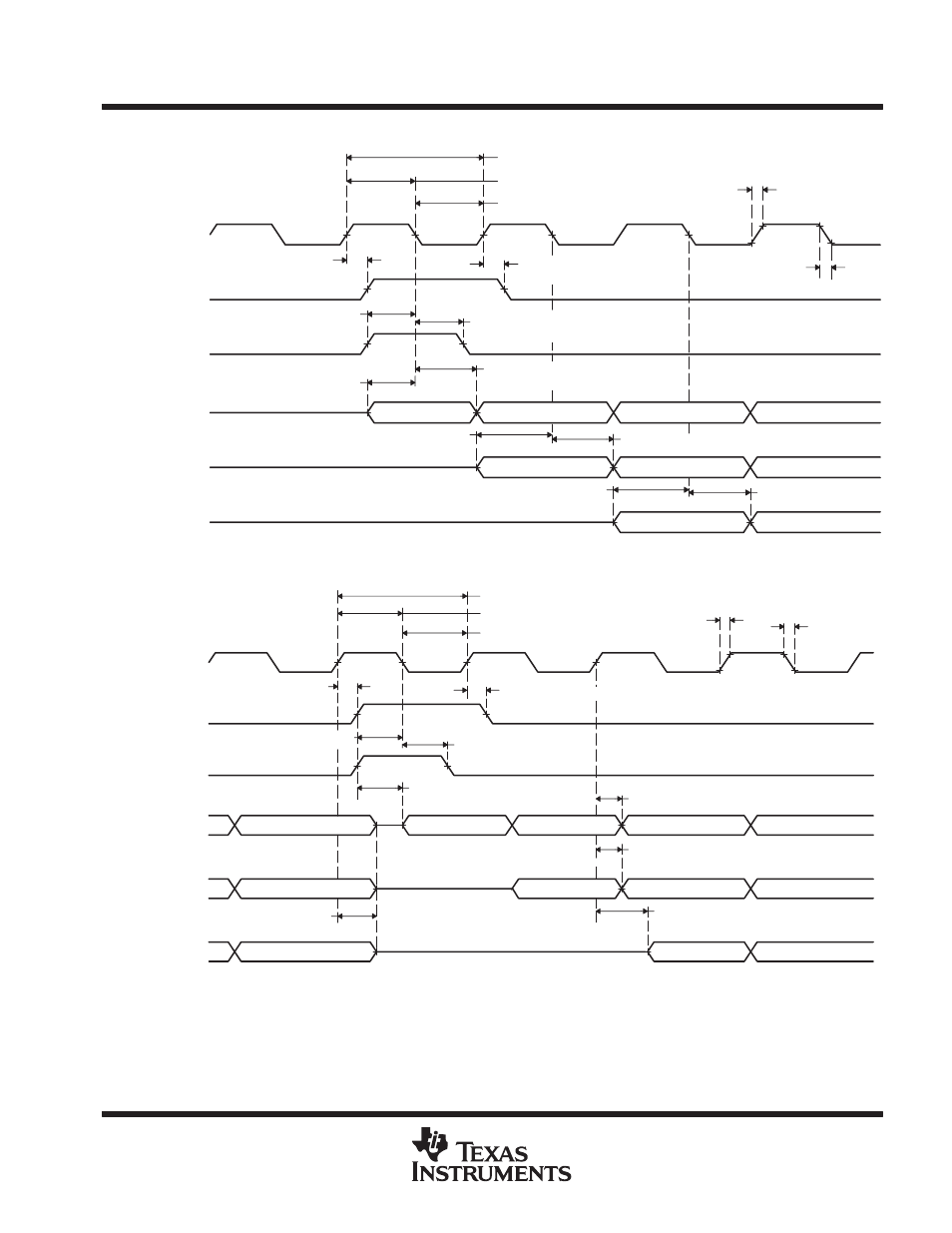

multichannel buffered serial port timing (continued)

(n–2)

Bit (n–1)

(n–3)

(n–2)

Bit (n–1)

(n–4)

(n–3)

(n–2)

Bit (n–1)

th(BCKRL–BDRV)

tsu(BDRV–BCKRL)

th(BCKRL–BDRV)

tsu(BDRV–BCKRL)

tsu(BDRV–BCKRL)

th(BCKRL–BDRV)

th(BCKRL–BFRH)

tsu(BFRH–BCKRL)

td(BCKRH–BFRV)

td(BCKRH–BFRV)

tr(BCKRX)

tr(BCKRX)

tw(BCKRXL)

tc(BCKRX)

tw(BCKRXH)

(RDATDLY=10b)

BDR

(RDATDLY=01b)

BDR

(RDATDLY=00b)

BDR

BFSR (ext)

BFSR (int)

BCLKR

Figure 28. McBSP Receive Timings

td(BCKXH–BDXV)

td(BCKXH–BDXV)

tdis(BCKXH–BDXHZ)

td(BCKXH–BDXV)

td(BDFXH–BDXV)

(XDATDLY=10b)

BDX

(XDATDLY=01b)

BDX

(XDATDLY=00b)

BDX

(n–2)

Bit (n–1)

Bit 0

(n–4)

Bit (n–1)

(n–3)

(n–2)

Bit 0

(n–3)

(n–2)

Bit (n–1)

Bit 0

th(BCKXL–BFXH)

tf(BCKRX)

tr(BCKRX)

tw(BCKRXL)

tc(BCKRX)

tw(BCKRXH)

BFSX (ext)

BFSX (int)

BCLKX

td(BCKXH–BFXV)

td(BCKXH–BFXV)

tsu(BFXH–BCKXL)

Figure 29. McBSP Transmit Timings