Dma subbank addressed registers (continued) – Texas Instruments TMS320VC5402 User Manual

Page 30

TMS320VC5402

FIXEDĆPOINT DIGITAL SIGNAL PROCESSOR

SPRS079E – OCTOBER 1998 – REVISED AUGUST 2000

30

POST OFFICE BOX 1443

•

HOUSTON, TEXAS 77251–1443

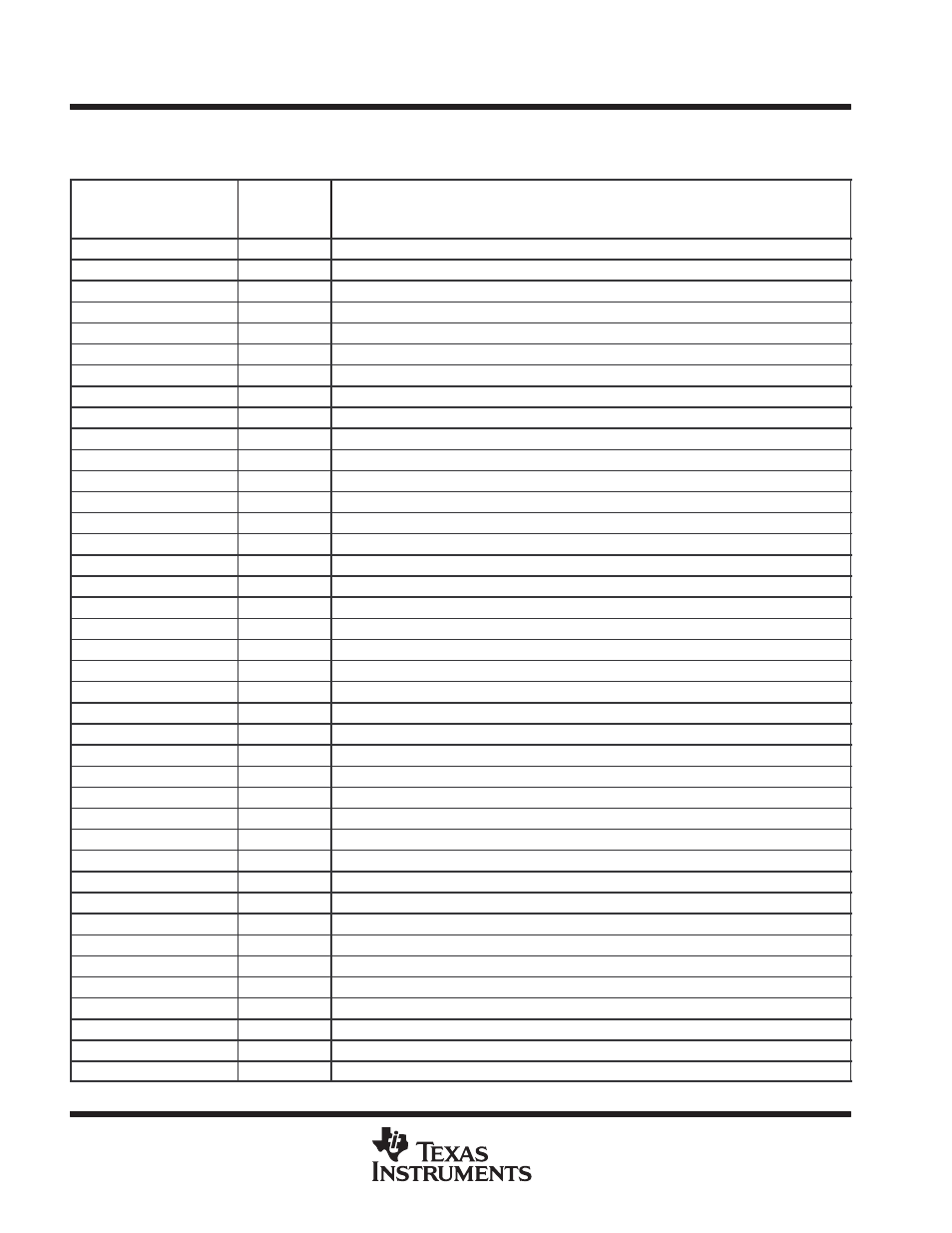

DMA subbank addressed registers (continued)

Table 12. DMA Subbank Addressed Registers

DMA

NAME

ADDRESS

SUB-

ADDRESS

DESCRIPTION

DMSRC0

56h/57h

БББББ

БББББ

00h

DMA channel 0 source address register

DMDST0

56h/57h

БББББ

БББББ

01h

DMA channel 0 destination address register

DMCTR0

56h/57h

БББББ

БББББ

02h

DMA channel 0 element count register

БББББ

БББББ

DMSFC0

ББББ

ББББ

56h/57h

БББББ

БББББ

03h

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA channel 0 sync select and frame count register

БББББ

БББББ

DMMCR0

ББББ

ББББ

56h/57h

БББББ

БББББ

04h

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA channel 0 transfer mode control register

БББББ

БББББ

DMSRC1

ББББ

ББББ

56h/57h

БББББ

БББББ

05h

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA channel 1 source address register

БББББ

БББББ

DMDST1

ББББ

ББББ

56h/57h

БББББ

БББББ

06h

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA channel 1 destination address register

БББББ

БББББ

DMCTR1

ББББ

ББББ

56h/57h

БББББ

БББББ

07h

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA channel 1 element count register

БББББ

DMSFC1

ББББ

56h/57h

БББББ

08h

БББББББББББББББББББББББ

DMA channel 1 sync select and frame count register

БББББ

БББББ

DMMCR1

ББББ

ББББ

56h/57h

БББББ

БББББ

09h

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA channel 1 transfer mode control register

БББББ

БББББ

DMSRC2

ББББ

ББББ

56h/57h

БББББ

БББББ

0Ah

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA channel 2 source address register

БББББ

БББББ

DMDST2

ББББ

ББББ

56h/57h

БББББ

БББББ

0Bh

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA channel 2 destination address register

БББББ

БББББ

DMCTR2

ББББ

ББББ

56h/57h

БББББ

БББББ

0Ch

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA channel 2 element count register

БББББ

БББББ

DMSFC2

ББББ

ББББ

56h/57h

БББББ

БББББ

0Dh

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA channel 2 sync select and frame count register

БББББ

БББББ

DMMCR2

ББББ

ББББ

56h/57h

БББББ

БББББ

0Eh

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA channel 2 transfer mode control register

БББББ

БББББ

DMSRC3

ББББ

ББББ

56h/57h

БББББ

БББББ

0Fh

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA channel 3 source address register

БББББ

DMDST3

ББББ

56h/57h

БББББ

10h

БББББББББББББББББББББББ

DMA channel 3 destination address register

БББББ

БББББ

DMCTR3

ББББ

ББББ

56h/57h

БББББ

БББББ

11h

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA channel 3 element count register

БББББ

БББББ

DMSFC3

ББББ

ББББ

56h/57h

БББББ

БББББ

12h

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA channel 3 sync select and frame count register

БББББ

БББББ

DMMCR3

ББББ

ББББ

56h/57h

БББББ

БББББ

13h

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA channel 3 transfer mode control register

БББББ

БББББ

DMSRC4

ББББ

ББББ

56h/57h

БББББ

БББББ

14h

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA channel 4 source address register

БББББ

БББББ

DMDST4

ББББ

ББББ

56h/57h

БББББ

БББББ

15h

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA channel 4 destination address register

БББББ

БББББ

DMCTR4

ББББ

ББББ

56h/57h

БББББ

БББББ

16h

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA channel 4 element count register

БББББ

БББББ

DMSFC4

ББББ

ББББ

56h/57h

БББББ

БББББ

17h

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA channel 4 sync select and frame count register

БББББ

БББББ

DMMCR4

ББББ

ББББ

56h/57h

БББББ

БББББ

18h

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA channel 4 transfer mode control register

БББББ

DMSRC5

ББББ

56h/57h

БББББ

19h

БББББББББББББББББББББББ

DMA channel 5 source address register

БББББ

БББББ

DMDST5

ББББ

ББББ

56h/57h

БББББ

БББББ

1Ah

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA channel 5 destination address register

БББББ

БББББ

DMCTR5

ББББ

ББББ

56h/57h

БББББ

БББББ

1Bh

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA channel 5 element count register

БББББ

БББББ

DMSFC5

ББББ

ББББ

56h/57h

БББББ

БББББ

1Ch

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA channel 5 sync select and frame count register

БББББ

БББББ

DMMCR5

ББББ

ББББ

56h/57h

БББББ

БББББ

1Dh

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA channel 5 transfer mode control register

БББББ

БББББ

DMSRCP

ББББ

ББББ

56h/57h

БББББ

БББББ

1Eh

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA source program page address (common channel)

БББББ

БББББ

DMDSTP

ББББ

ББББ

56h/57h

БББББ

БББББ

1Fh

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA destination program page address (common channel)

БББББ

БББББ

DMIDX0

ББББ

ББББ

56h/57h

БББББ

БББББ

20h

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA element index address register 0

БББББ

DMIDX1

ББББ

56h/57h

БББББ

21h

БББББББББББББББББББББББ

DMA element index address register 1

БББББ

БББББ

DMFRI0

ББББ

ББББ

56h/57h

БББББ

БББББ

22h

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA frame index register 0

БББББ

БББББ

DMFRI1

ББББ

ББББ

56h/57h

БББББ

БББББ

23h

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA frame index register 1

БББББ

БББББ

DMGSA

ББББ

ББББ

56h/57h

БББББ

БББББ

24h

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA global source address reload register

БББББ

БББББ

DMGDA

ББББ

ББББ

56h/57h

БББББ

БББББ

25h

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA global destination address reload register

БББББ

БББББ

DMGCR

ББББ

ББББ

56h/57h

БББББ

БББББ

26h

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA global count reload register

БББББ

БББББ

DMGFR

ББББ

ББББ

56h/57h

БББББ

БББББ

27h

БББББББББББББББББББББББ

БББББББББББББББББББББББ

DMA global frame count reload register