Texas Instruments TMS320VC5402 User Manual

Page 48

TMS320VC5402

FIXEDĆPOINT DIGITAL SIGNAL PROCESSOR

SPRS079E – OCTOBER 1998 – REVISED AUGUST 2000

48

POST OFFICE BOX 1443

•

HOUSTON, TEXAS 77251–1443

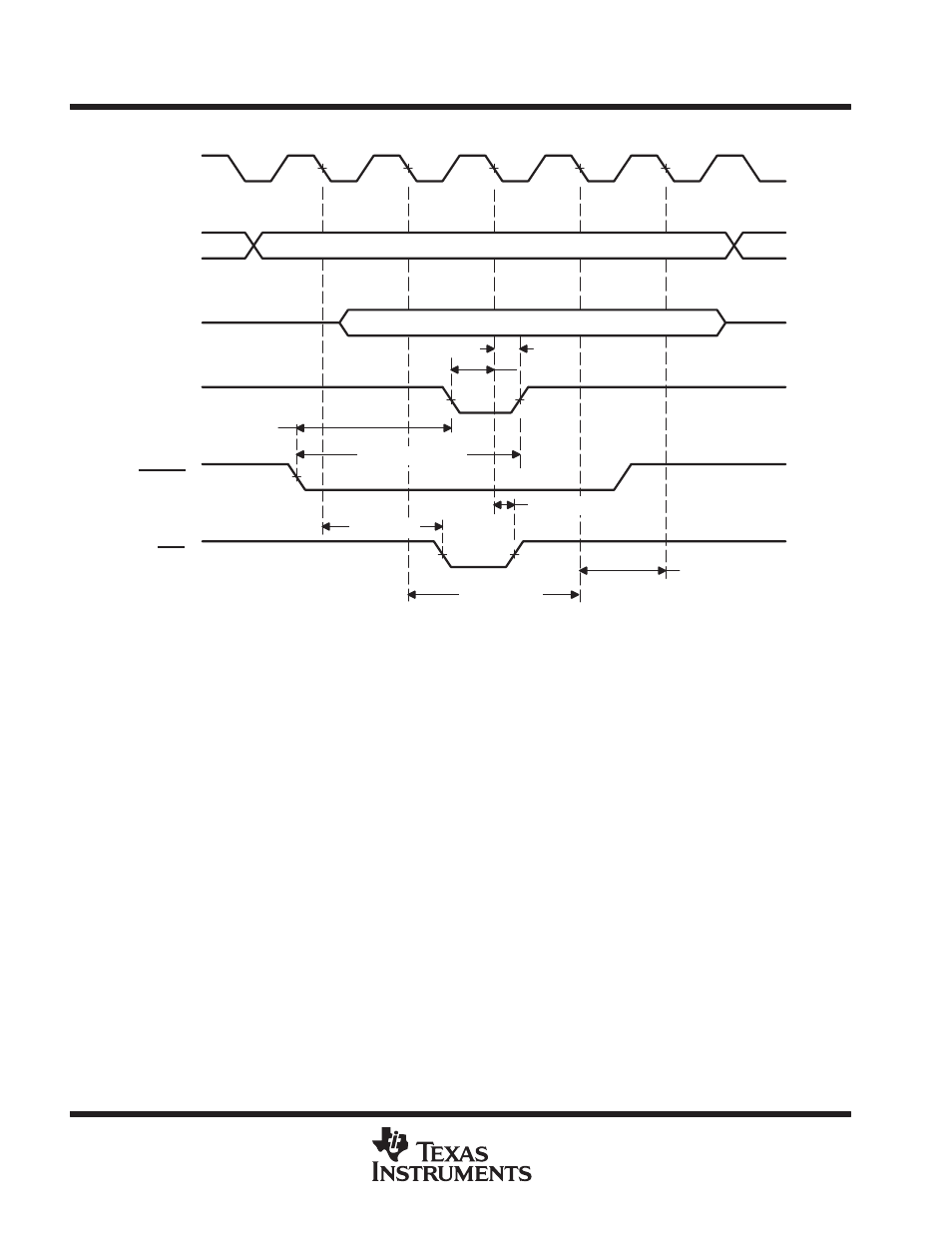

ready timing for externally generated wait states (continued)

IOSTRB

MSC

READY

D[15:0]

A[19:0]

CLKOUT

th(RDY)

Wait State Generated

by READY

Wait States

Generated

Internally

tv(RDY)IOSTRB

tsu(RDY)

tv(MSCH)

tv(MSCL)

th(RDY)IOSTRB

NOTE A: A[19:16] are always driven low during accesses to I/O space.

Figure 20. I/O Write With Externally Generated Wait States