Mcbsp control registers and subaddresses, Dma subbank addressed registers – Texas Instruments TMS320VC5402 User Manual

Page 29

TMS320VC5402

FIXEDĆPOINT DIGITAL SIGNAL PROCESSOR

SPRS079E – OCTOBER 1998 – REVISED AUGUST 2000

29

POST OFFICE BOX 1443

•

HOUSTON, TEXAS 77251–1443

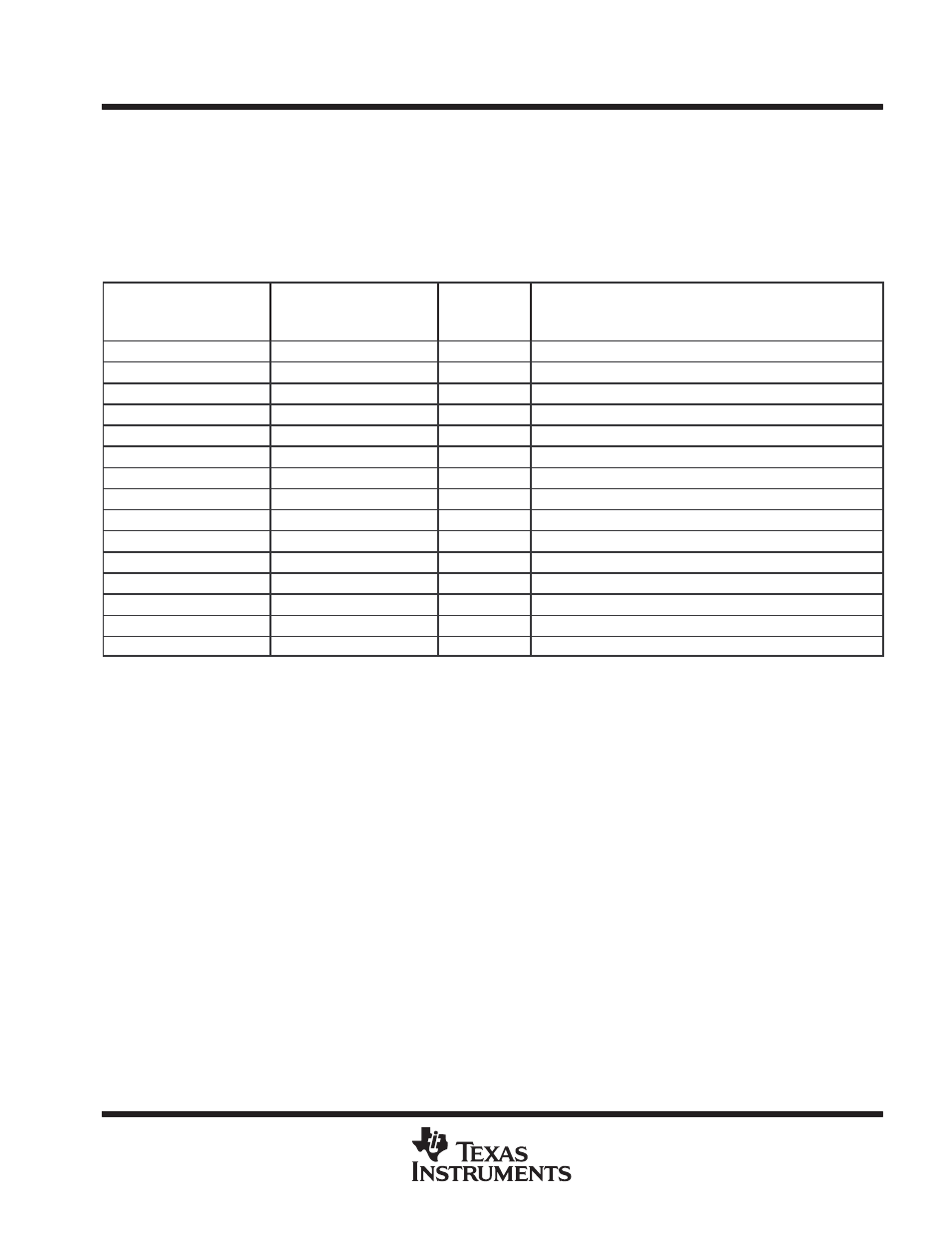

McBSP control registers and subaddresses

The control registers for the multichannel buffered serial port (McBSP) are accessed using the subbank

addressing scheme. This allows a set or subbank of registers to be accessed through a single memory location.

The serial port subbank address (SPSA) register is used as a pointer to select a particular register within the

subbank. The serial port subbank data (SPSD) register is used to access (read or write) the selected register.

Table 11 shows the McBSP control registers and their corresponding sub-addresses.

Table 11. McBSP Control Registers and Subaddresses

McBSP0

McBSP1

NAME

ADDRESS

NAME

ADDRESS

SUB-

ADDRESS

DESCRIPTION

БББББ

БББББ

SPCR10

ББББ

ББББ

39h

БББББ

БББББ

SPCR11

ББББ

ББББ

49h

БББББ

БББББ

00h

БББББББББББББББ

БББББББББББББББ

Serial port control register 1

БББББ

SPCR20

ББББ

39h

БББББ

SPCR21

ББББ

49h

БББББ

01h

БББББББББББББББ

Serial port control register 2

БББББ

БББББ

RCR10

ББББ

ББББ

39h

БББББ

БББББ

RCR11

ББББ

ББББ

49h

БББББ

БББББ

02h

БББББББББББББББ

БББББББББББББББ

Receive control register 1

БББББ

БББББ

RCR20

ББББ

ББББ

39h

БББББ

БББББ

RCR21

ББББ

ББББ

49h

БББББ

БББББ

03h

БББББББББББББББ

БББББББББББББББ

Receive control register 2

БББББ

БББББ

XCR10

ББББ

ББББ

39h

БББББ

БББББ

XCR11

ББББ

ББББ

49h

БББББ

БББББ

04h

БББББББББББББББ

БББББББББББББББ

Transmit control register 1

БББББ

БББББ

XCR20

ББББ

ББББ

39h

БББББ

БББББ

XCR21

ББББ

ББББ

49h

БББББ

БББББ

05h

БББББББББББББББ

БББББББББББББББ

Transmit control register 2

БББББ

БББББ

SRGR10

ББББ

ББББ

39h

БББББ

БББББ

SRGR11

ББББ

ББББ

49h

БББББ

БББББ

06h

БББББББББББББББ

БББББББББББББББ

Sample rate generator register 1

БББББ

БББББ

SRGR20

ББББ

ББББ

39h

БББББ

БББББ

SRGR21

ББББ

ББББ

49h

БББББ

БББББ

07h

БББББББББББББББ

БББББББББББББББ

Sample rate generator register 2

БББББ

БББББ

MCR10

ББББ

ББББ

39h

БББББ

БББББ

MCR11

ББББ

ББББ

49h

БББББ

БББББ

08h

БББББББББББББББ

БББББББББББББББ

Multichannel register 1

БББББ

БББББ

MCR20

ББББ

ББББ

39h

БББББ

БББББ

MCR21

ББББ

ББББ

49h

БББББ

БББББ

09h

БББББББББББББББ

БББББББББББББББ

Multichannel register 2

БББББ

RCERA0

ББББ

39h

БББББ

RCERA1

ББББ

49h

БББББ

0Ah

БББББББББББББББ

Receive channel enable register partition A

БББББ

БББББ

RCERB0

ББББ

ББББ

39h

БББББ

БББББ

RCERB1

ББББ

ББББ

49h

БББББ

БББББ

0Bh

БББББББББББББББ

БББББББББББББББ

Receive channel enable register partition B

БББББ

БББББ

XCERA0

ББББ

ББББ

39h

БББББ

БББББ

XCERA1

ББББ

ББББ

49h

БББББ

БББББ

0Ch

БББББББББББББББ

БББББББББББББББ

Transmit channel enable register partition A

БББББ

БББББ

XCERB0

ББББ

ББББ

39h

БББББ

БББББ

XCERB1

ББББ

ББББ

49h

БББББ

БББББ

0Dh

БББББББББББББББ

БББББББББББББББ

Transmit channel enable register partition B

БББББ

БББББ

PCR0

ББББ

ББББ

39h

БББББ

БББББ

PCR1

ББББ

ББББ

49h

БББББ

БББББ

0Eh

БББББББББББББББ

БББББББББББББББ

Pin control register

DMA subbank addressed registers

The direct memory access (DMA) controller has several control registers associated with it. The main control

register (DMPREC) is a standard memory-mapped register. However, the other registers are accessed using

the subbank addressing scheme. This allows a set or subbank of registers to be accessed through a single

memory location. The DMA subbank address (DMSA) register is used as a pointer to select a particular register

within the subbank, while the DMA subbank data (DMSDN) register or the DMA subbank data register with

autoincrement (DMSDI) is used to access (read or write) the selected register.

When the DMSDI register is used to access the subbank, the subbank address is automatically

post-incremented so that a subsequent access affects the next register within the subbank. This autoincrement

feature is intended for efficient, successive accesses to several control registers. If the autoincrement feature

is not required, the DMSDN register should be used to access the subbank. Table 12 shows the DMA controller

subbank addressed registers and their corresponding subaddresses.