Texas Instruments TMS320VC5402 User Manual

Page 28

TMS320VC5402

FIXEDĆPOINT DIGITAL SIGNAL PROCESSOR

SPRS079E – OCTOBER 1998 – REVISED AUGUST 2000

28

POST OFFICE BOX 1443

•

HOUSTON, TEXAS 77251–1443

memory-mapped registers (continued)

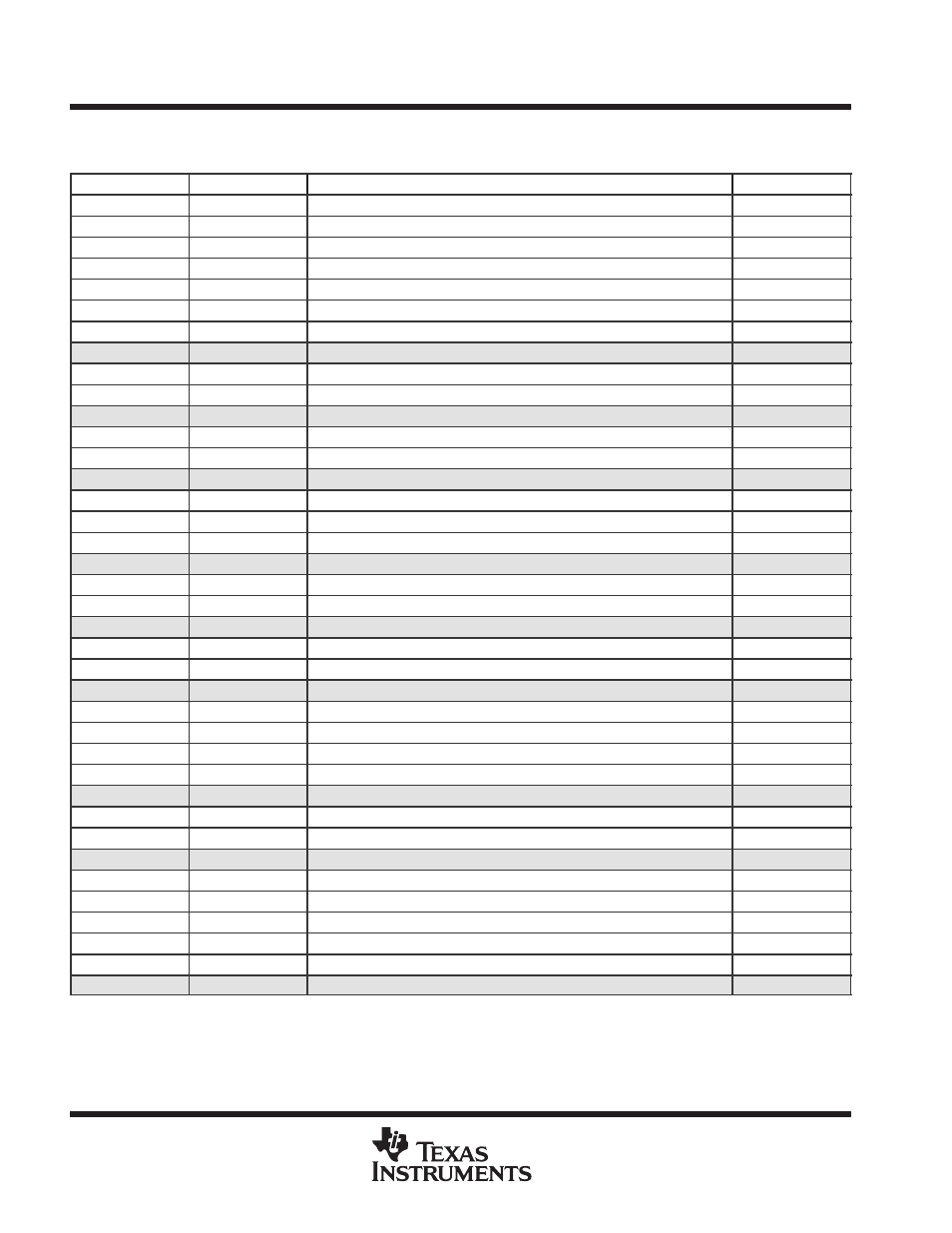

Table 10. Peripheral Memory-Mapped Registers

NAME

ADDRESS

DESCRIPTION

TYPE

DRR20

20h

БББББББББББББББББББ

БББББББББББББББББББ

McBSP0 data receive register 2

McBSP #0

DRR10

21h

БББББББББББББББББББ

БББББББББББББББББББ

McBSP0 data receive register 1

McBSP #0

DXR20

22h

БББББББББББББББББББ

БББББББББББББББББББ

McBSP0 data transmit register 2

McBSP #0

DXR10

23h

БББББББББББББББББББ

БББББББББББББББББББ

McBSP0 data transmit register 1

McBSP #0

TIM

24h

БББББББББББББББББББ

БББББББББББББББББББ

Timer0 register

Timer0

PRD

25h

БББББББББББББББББББ

БББББББББББББББББББ

Timer0 period counter

Timer0

TCR

26h

БББББББББББББББББББ

БББББББББББББББББББ

Timer0 control register

Timer0

–

27h

Reserved

SWWSR

28h

БББББББББББББББББББ

БББББББББББББББББББ

Software wait-state register

External Bus

BSCR

29h

БББББББББББББББББББ

Bank-switching control register

External Bus

–

2Ah

Reserved

SWCR

2Bh

БББББББББББББББББББ

БББББББББББББББББББ

Software wait-state control register

External Bus

HPIC

2Ch

БББББББББББББББББББ

БББББББББББББББББББ

HPI control register

HPI

–

2Dh–2Fh

Reserved

TIM1

30h

БББББББББББББББББББ

БББББББББББББББББББ

Timer1 register

Timer1

PRD1

31h

БББББББББББББББББББ

БББББББББББББББББББ

Timer1 period counter

Timer1

TCR1

32h

БББББББББББББББББББ

БББББББББББББББББББ

Timer1 control register

Timer1

–

33h–37h

Reserved

ББББББ

ББББББ

SPSA0

ББББББ

ББББББ

38h

БББББББББББББББББББ

БББББББББББББББББББ

McBSP0 subbank address register†

ББББББ

ББББББ

McBSP #0

ББББББ

ББББББ

SPSD0

ББББББ

ББББББ

39h

БББББББББББББББББББ

БББББББББББББББББББ

McBSP0 subbank data register†

ББББББ

ББББББ

McBSP #0

–

3Ah–3Bh

Reserved

ББББББ

ББББББ

GPIOCR

ББББББ

ББББББ

3Ch

БББББББББББББББББББ

БББББББББББББББББББ

General-purpose I/O pins control register

ББББББ

ББББББ

GPIO

ББББББ

ББББББ

GPIOSR

ББББББ

ББББББ

3Dh

БББББББББББББББББББ

БББББББББББББББББББ

General-purpose I/O pins status register

ББББББ

ББББББ

GPIO

–

3Eh–3Fh

Reserved

DRR21

40h

БББББББББББББББББББ

БББББББББББББББББББ

McBSP1 data receive register 2

McBSP #1

DRR11

41h

БББББББББББББББББББ

БББББББББББББББББББ

McBSP1 data receive register 1

McBSP #1

DXR21

42h

БББББББББББББББББББ

McBSP1 data transmit register 2

McBSP #1

DXR11

43h

БББББББББББББББББББ

БББББББББББББББББББ

McBSP1 data transmit register 1

McBSP #1

–

44h–47h

Reserved

SPSA1

48h

БББББББББББББББББББ

БББББББББББББББББББ

McBSP1 subbank address register†

McBSP #1

ББББББ

ББББББ

SPSD1

ББББББ

ББББББ

49h

БББББББББББББББББББ

БББББББББББББББББББ

McBSP1 subbank data register†

ББББББ

ББББББ

McBSP #1

–

4Ah–53h

Reserved

DMPREC

54h

БББББББББББББББББББ

БББББББББББББББББББ

DMA channel priority and enable control register

DMA

DMSA

55h

БББББББББББББББББББ

БББББББББББББББББББ

DMA subbank address register‡

DMA

ББББББ

ББББББ

DMSDI

ББББББ

ББББББ

56h

БББББББББББББББББББ

БББББББББББББББББББ

DMA subbank data register with autoincrement‡

ББББББ

ББББББ

DMA

ББББББ

ББББББ

DMSDN

ББББББ

ББББББ

57h

БББББББББББББББББББ

БББББББББББББББББББ

DMA subbank data register‡

ББББББ

ББББББ

DMA

ББББББ

ББББББ

CLKMD

ББББББ

ББББББ

58h

БББББББББББББББББББ

БББББББББББББББББББ

Clock mode register

ББББББ

ББББББ

PLL

–

59h–5Fh

Reserved

† See Table 11 for a detailed description of the McBSP control registers and their sub-addresses.

‡ See Table 12 for a detailed description of the DMA subbank addressed registers.