15 audio (s/pdif / i2s) interface, Table 17, Audio (s/pdif / i – Marvel Group Integrated Controller 88F6281 User Manual

Page 40: 15 audio (s/pdif / i, S) interface

88F6281

Hardware Specifications

Doc. No. MV-S104859-U0 Rev. E

Copyright © 2008 Marvell

Page 40

Document Classification: Proprietary Information

December 2, 2008, Preliminary

1.2.15

Audio (S/PDIF / I

2

S) Interface

Note

All of the Audio signals are multiplexed on the MPP pins (see

If the Audio interface is not used, leave all of the signals unconnected.

The Audio signals are powered on VDDO or on VDD_GE_B, based on the pin

multiplexing option.

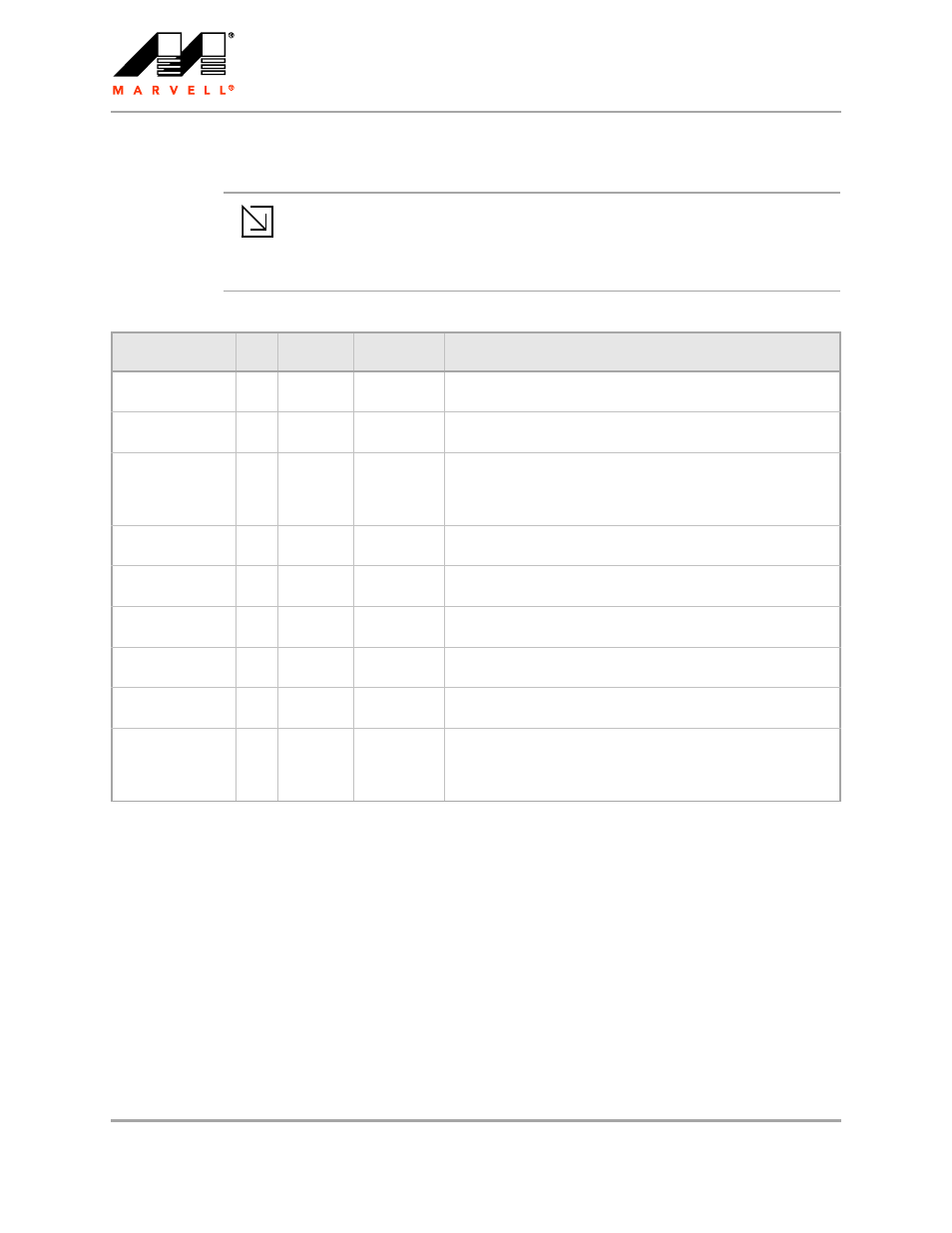

Table 17: Audio (S/PDIF / I

2

S) Interface Signal Assignment

P i n N a m e

I / O

P i n

Ty p e

P o w e r

R a i l

D e s c r i p t i o n

AU_SPDIFI

I

CMOS VDDO/

VDD_GE_B

S/PDIF In

AU_SPDIFO

O

CMOS VDDO/

VDD_GE_B

S/PDIF Out

AU_

SPDFRMCLK

O

CMOS VDDO/

VDD_GE_B

S/PDIF Recovered Master Clock (256 x F

s

)

1

For the frequency of this clock, see the Audio External

Reference Clock section of

Timing Specifications, on page 86

.

AU_I2SBCLK

O

CMOS VDDO/

VDD_GE_B

I

2

S Bit Clock (64 x F

s

)

AU_I2SDO

O

CMOS VDDO/

VDD_GE_B

Transmitter Data Out

AU_I2SLRCLK

O

CMOS VDDO/

VDD_GE_B

I

2

S Left/Right Clock (1 x F

s

)

AU_I2SMCLK

O

CMOS VDDO/

VDD_GE_B

I

2

S Master Clock (256 x F

s

)

AU_I2SDI

I

CMOS

VDDO/

VDD_GE_B

I

2

S Receiver Data In

AU_EXTCLK

I

CMOS

VDDO/

VDD_GE_B

External Audio Clock

For the frequency of this clock, see the Audio External

Reference Clock section of

Timing Specifications, on page 86

.

1. F

s

is the audio sample rate.