Sundance SMT916 User Manual

Page 14

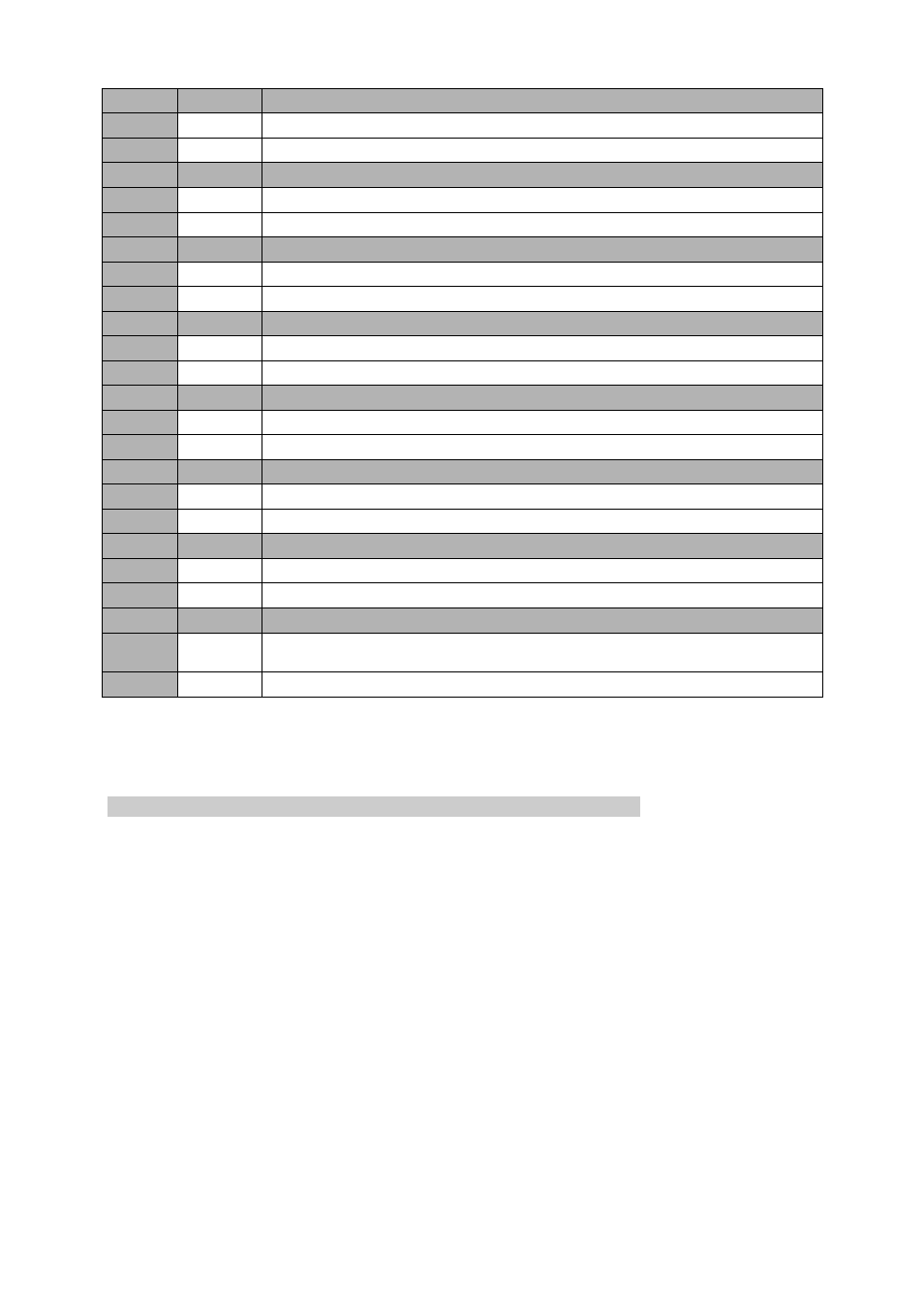

Setting

Bit 7

Description – ADC7 Enable

0

0

ADC7 interface is disabled.

1

1

Normal Mode of Operation – ADC7 interface is enabled.

Setting

Bit 8

Description – ADC8 Enable

0

0

ADC8 interface is disabled.

1

1

Normal Mode of Operation – ADC8 interface is enabled.

Setting

Bit 9

Description – ADC9 Enable

0

0

ADC9 interface is disabled.

1

1

Normal Mode of Operation – ADC9 interface is enabled.

Setting

Bit 10

Description – ADC10 Enable

0

0

ADC10 interface is disabled.

1

1

Normal Mode of Operation – ADC10 interface is enabled.

Setting

Bit 11

Description – ADC11 Enable

0

0

ADC11 interface is disabled.

1

1

Normal Mode of Operation – ADC11 interface is enabled.

Setting

Bit 13

Description – External Clock Out Enable

0

0 Disabled.

1

1

External Clock Output Enabled.

Setting

Bit 14

Description – External Clock PLL Lock status

0

0

PLL not locked.

1

1 PLL

locked.

Setting

Bit 15

Description – Clock Source Selection

0

0

FPGA Clock (on-board 25-MHz clock) )used to generate conversion rate and capture clock

(system clock).

1

1

External Clock used to generate conversion rate and capture clock (system clock).

Note that ADC0 enable bit also enables the conversion signal for group a. Same

applies to ADC6 for group b of ADCs.

3.4.4 Conversion rate register channels 0 to 5 – 0x10.

A 12-bit register is implemented in the firmware in order to define the sampling

frequency of the ADCs. There is one per group of 6 ADCs, so top and bottom ADCs

can work at different rates.

The sampling frequency registers must be loaded with a multiple of 4ns that makes

the sampling period. The block implemented in the FPGA is clocked at 250MHz,

hence the 4ns step.

For instance, a 100ns sampling period (equivalent to 10MHz sampling frequency)

would require loading in the register a value of 100/4=25 (that’s 0x19 -

hexadecimal).

ADCs work at a minimum sampling period of 100ns and a maximum of 10000ns,

defining a range of values for the registers of 25 (0x19) to 2500 (0x9C4).

The first 4 values of the counter enable the conversion signal, which therefore stays

high for 16ns. It remains low until the entire cycle is completed. The duty cycle

follows the AD9676 specifications.