Sundance SMT916 User Manual

Page 13

1

1

PLL in reset mode. Does not auto-clear..

Setting

Bit 15

Description – Clock Source Selection

0

0

FPGA Clock (on-board 25-MHz clock) )used to generate conversion rate and capture clock

(system clock).

1

1

External Clock used to generate conversion rate and capture clock (system clock).

Note that ADC0 enable bit also enables the conversion signal for group a. Same

applies to ADC6 for group b of ADCs.

The PLL reset (External clock) can be needed when switching to external clock in

order to force the PLL to lock. The Lock status can be read from the Global Status

Register.

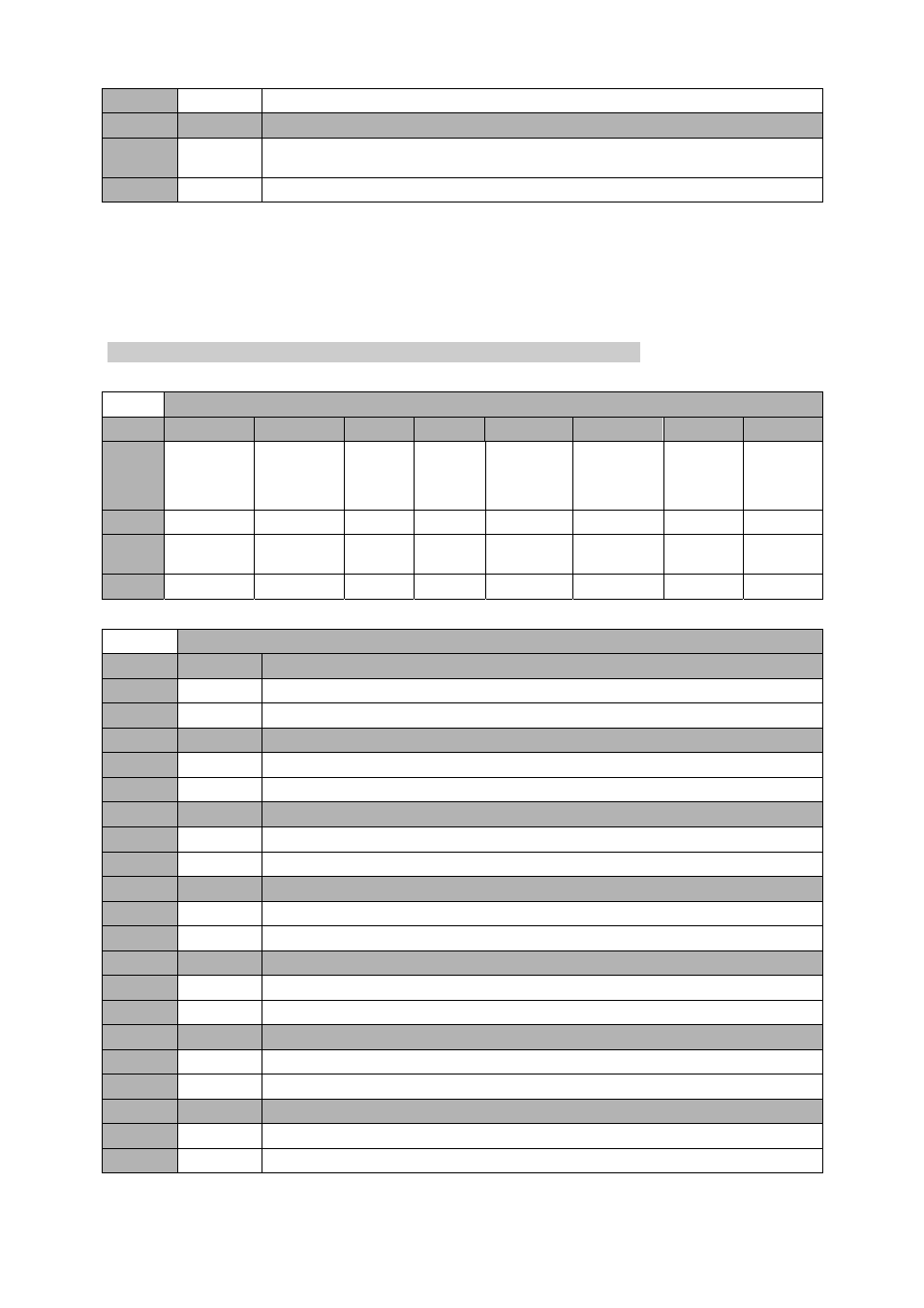

3.4.3 Global Status Register – 0x4

Global Status Register – 0x4 (Read-only register).

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

1

Clock

Source

Selection

External

PLL Locked

External

Clock

Output

Enable

Reserved

ADC11

Enable

ADC10

Enable

ADC9

Enable

ADC8

Enable

Default

‘0’ ‘0’

‘0’

‘0’

‘0’ ‘0’ ‘0’

‘0’

0

ADC7

Enable

ADC6

Enable

ADC5

Enable

ADC4

Enable

ADC3

Enable

ADC2

Enable

ADC1

Enable

ADC0

Enable

Default

‘0’ ‘0’

‘0’

‘0’

‘0’ ‘0’ ‘0’

‘0’

Global control Register – 0x4 (Write register).

Setting

Bit 0

Description – ADC0 Enable

0

0

ADC0 interface is disabled.

1

1

Normal Mode of Operation – ADC0 interface is enabled.

Setting

Bit 1

Description – ADC1 Enable

0

0

ADC1 interface is disabled.

1

1

Normal Mode of Operation – ADC1 interface is enabled.

Setting

Bit 2

Description – ADC2 Enable

0

0

ADC2 interface is disabled.

1

1

Normal Mode of Operation – ADC2 interface is enabled.

Setting

Bit 3

Description – ADC3 Enable

0

0

ADC3 interface is disabled.

1

1

Normal Mode of Operation – ADC3 interface is enabled.

Setting

Bit 4

Description – ADC4 Enable

0

0

ADC4 interface is disabled.

1

1

Normal Mode of Operation – ADC4 interface is enabled.

Setting

Bit 5

Description – ADC5 Enable

0

0

ADC5 interface is disabled.

1

1

Normal Mode of Operation – ADC5 interface is enabled.

Setting

Bit 6

Description – ADC6 Enable

0

0

ADC6 interface is disabled.

1

1

Normal Mode of Operation – ADC6 interface is enabled.