7 sundance digital bus (sdb), Sundance digital bus (sdb), Table 5 : sdb control register – Sundance SMT310 v.1.6 User Manual

Page 15

User Manual (QCF42); Version 3.0, 8/11/00; © Sundance Multiprocessor Technology Ltd. 1999

7 Sundance Digital Bus (SDB)

A growing number of Sundance’s Modules have an on-board SDB. The SDB is

.

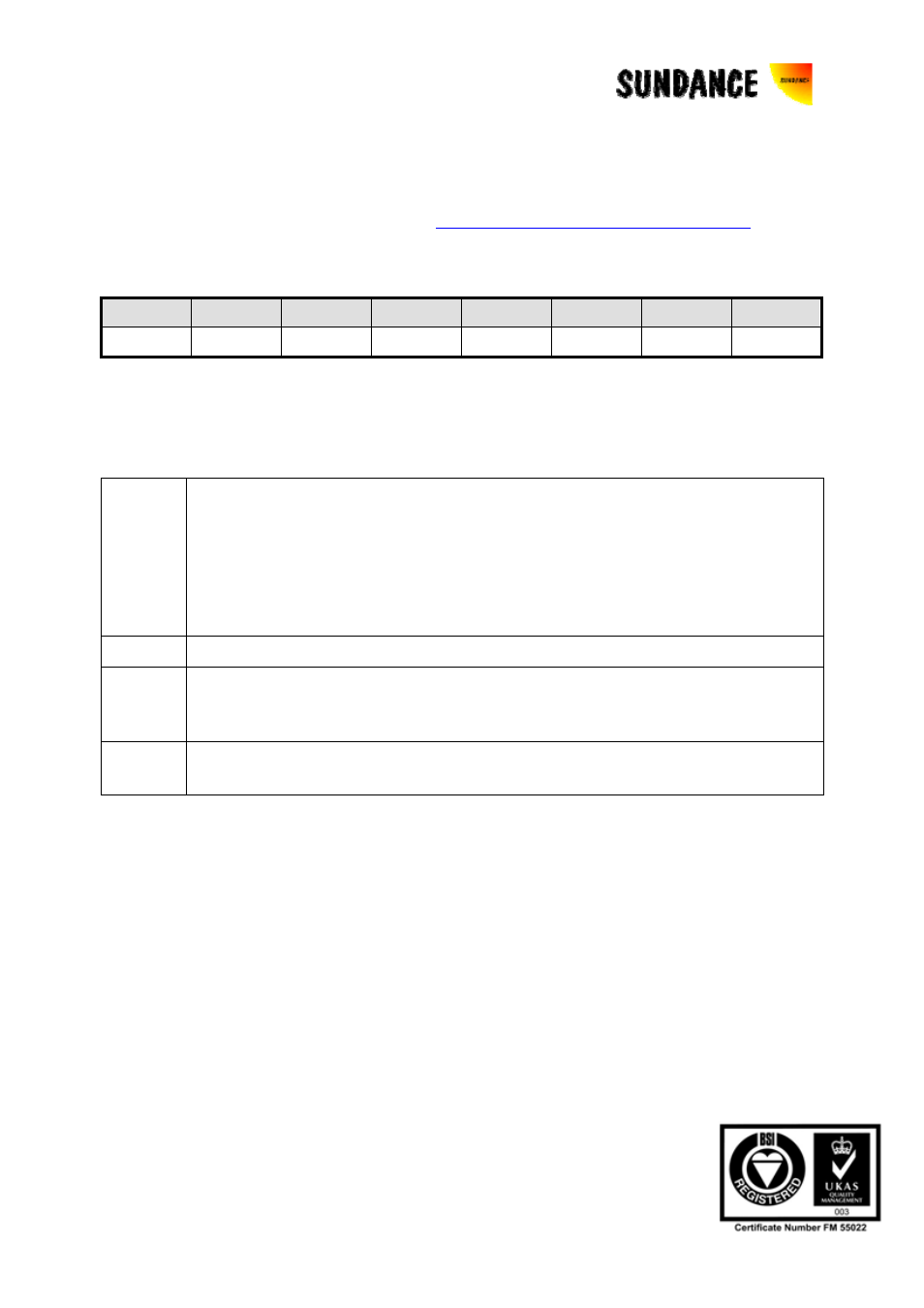

The following register controls the carrier’s SDB.

D7

D6

D5

D4

D3

D2

D1

D0

X X

OFFF

IPFF

RW

RW

RW

RXNTX

Table 5 : SDB Control Register

The SDB control and status register is located at BAR2 offset 0x00200260. The bit

definitions are shown below:

RXNTX

SDB Direction. The SDB direction is set using Jumper J8 (

Figure 9 : Jumper Finder Diagram) on the SMT310, When the jumper is

out the SDB is set for receive mode; when the jumper is in the SDB is set

for transmit mode. This bit indicates the direction set: 0=Receive,

1=Transmit.

RW

General scratch bits

IPFF

Input FIFO full: When set, a 16-bit value has been latched in the data

register ready for reading. This bit is automatically cleared on a read from

the data register.

OPFF

Output FIFO full: This bit is set when a 16-bit value is written to the FIFO

and is automatically cleared when it has been sent out of the SDB.

The SDB data register is located at BAR2 offset 0x00200240. You can write 16-bit

values to this location to transfer them over the SDB interface as long as the OPFF

flag in the status register is clear and J8 jumper is in.