Sundance PARS User Manual

Page 14

Revision 11-wip-7

Page 14 of 70

Sundance Digital Signal Processing, Inc.

4790 Caughlin Parkway 233, Reno, NV 89519-0907, U.S.A.

email:

Tel: +1 (775) 827-3103

www.sundancedsp.com

link-layer drivers in support of Diamond must be configured prior to attempting to run on

hardware. PARS provides an interface to link-layer drivers based on Diamond’s example

TIS project

4

.

PARS

The MathWorks

TI

Xilinx

Diamond/DSP Diamond/FPGA

DSP

FPGA Simulink

RTW

RTW-EC

HDLCoder CCS ISE

Sysgen Single Multi Single

Multi

Single None

R

R

O

N/A

R

N/A

N/A

R

O

N/A

N/A

Single Single

R

R

O

O

R

R

O

R

O

R

O

Single Multi

R

R

O

O

R

R

O

R

O

N/A

R

None

Any

Not Available in PARS 11

Multi

None

R

R

O

N/A

R

N/A

N/A

N/A

R

N/A

N/A

Multi

Single

R

R

O

O

R

R

O

N/A

R

R

O

Multi

Multi

R

R

O

O

R

R

O

N/A

R

N/A

R

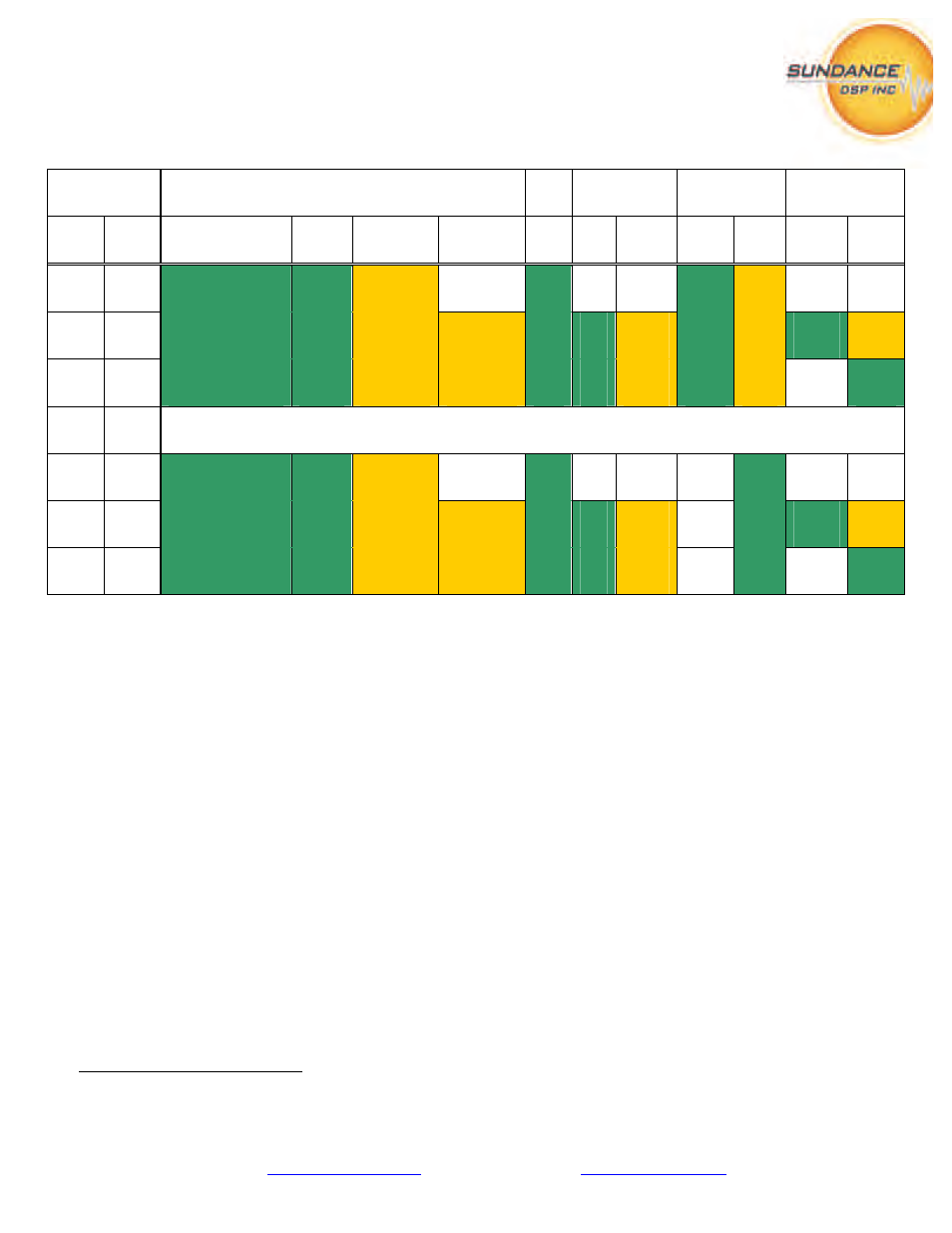

Table 1 - Matrix of PARS features vs. tools required

The table above summarizes the required tools with respect to the desired number of DSPs and FPGAs.

An ‘R’ indicates a required tool. ‘O’ indicates an optional tool. ‘N/A’ indicates the tool does not

apply.

2.3.

DEVELOPMENT FLOW

Generally speaking, developing with PARS is very similar to developing in Simulink®. A ‘PARS’

model is a fully-featured Simulink® model, with one important caveat: Prior to initiating code

generation, all blocks on the top level model must be organized into subsystems which have been

assigned to a processor type using the PARS Control Panel.

Organizing blocks into subsystems does not alter their behaviour in any way, so the model remains true

to the original. Assigning a subsystem to a processor type using PARS, causes the subsystem to be

‘masked’ and provides a means to control attributes for that subsystem with respect to the type of

processor you have assigned.

4

See: %DIAMOND_ROOT%\server\examples\TIS for additional details.