6 four- bit digital i/o registers, 7 status register – Measurement Computing CIO-DAS16/330 User Manual

Page 15

Bits 3-0 contain the starting channel number and bits 7-4 contain the ending channel number. If you wanted to scan

channels 1, 2, 3 in that order, you could do so by placing the 3 in bits 7-4 and the 1 in bits 3-0.

NOTE

Every write to this register sets the current A/D channel MUX setting to the number in bits 0-3. See

BASE + 8. Every write to this register clears the FIFO buffer.

4.6 FOUR- BIT DIGITAL I/O REGISTERS

BASE ADDRESS +3

When read...

DI0,

TRIG

DI1

DI2,

CTR0

GATE

DI3

0

0

0

0

0

1

2

3

4

5

6

7

READ

The signals present at the inputs are read as one byte, the most significant four bits of which are always zero. The

pins 25 (digital input 0) and 24 (digital input 2) digital inputs have two functions each.

The TRIG function of digital input 0 may be used to hold off the first sample of an A/D set by holding it low (0V)

until you are ready to take samples, which are then paced by the 8254. It can also be used as the source of an external

start conversion pulse, synchronizing A/D conversions to some external event.

When written to...

DO0

DO1

DO2

DO3

X

X

X

X

0

1

2

3

4

5

6

7

WRITE

The upper four bits are ignored. The lower four bits are latched TTL outputs. Once written, the state of the inputs

cannot be read back because a read back would read the separate digital input lines (see above).

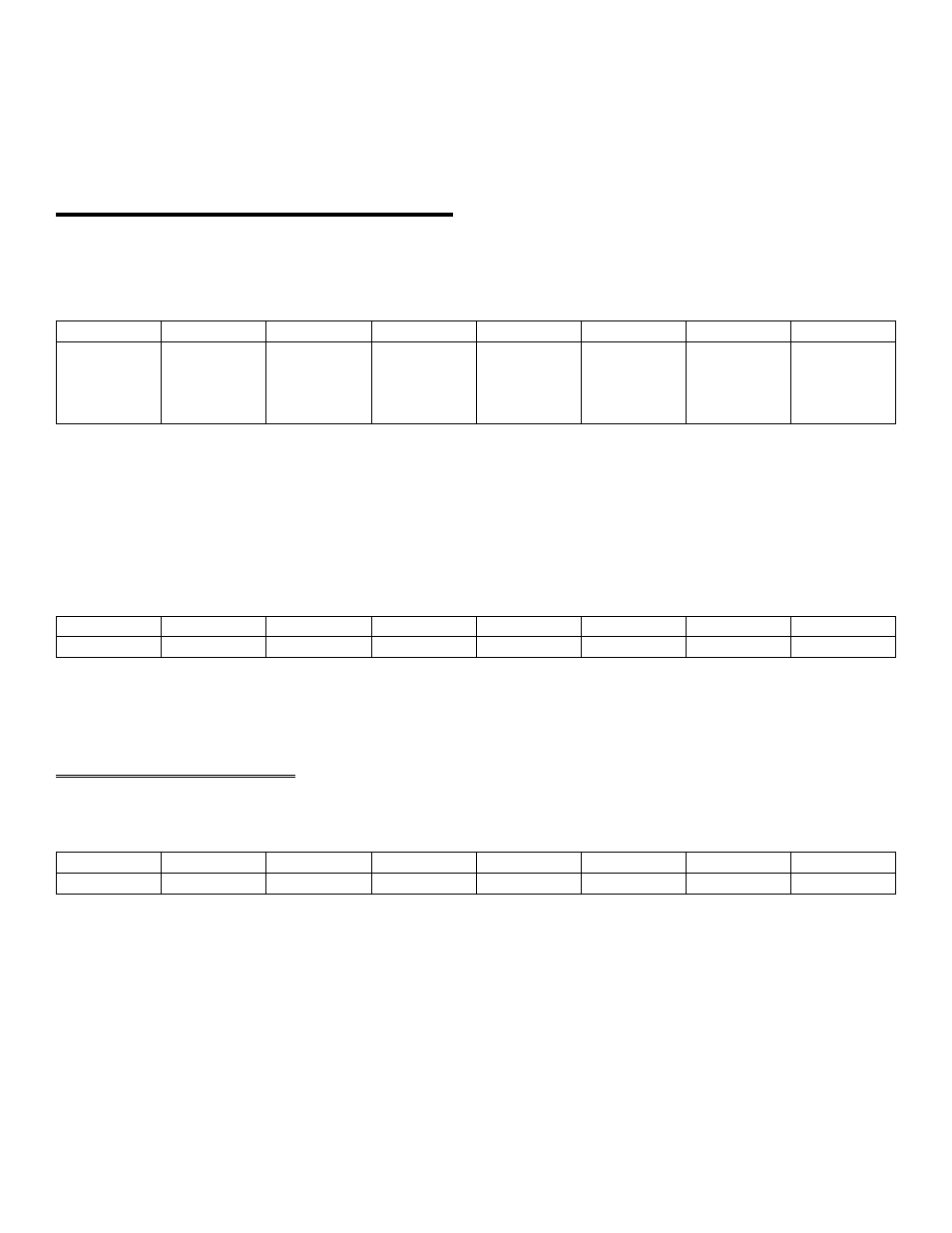

4.7 STATUS REGISTER

BASE ADDRESS +8

CH1

CH2

CH4

CH8

INT

MUX

U/B

EOC

0

1

2

3

4

5

6

7

A read mostly, one-function-write register.

READ

EOC = 1, the A/D converter is busy. EOC = 0, it is free.

U/B = 1, the amplifier is in Unipolar mode. U/B = 0, is bipolar.

MUX = 1, Channels are configured 16 single ended. MUX = 0, 8 differential.

INT = 1, an external pulse has been received. INT = 0, the flip-flop is ready to receive a pulse.

There is a flip-flop on the TRIGGER input (pin 25) which will latch a pulse as short as 200 ns. After being triggered, this

flip-flop must be reset by a write to this register. Your interrupt service routine must do this before another interrupt

trigger can be received.

11