Connector 1 connector 2, Peripheral bus connector i/o connector – Zilog EZ80190 User Manual

Page 76

UM014108-0810

Schematic Diagrams

eZ80190 Development Kit

User Manual

72

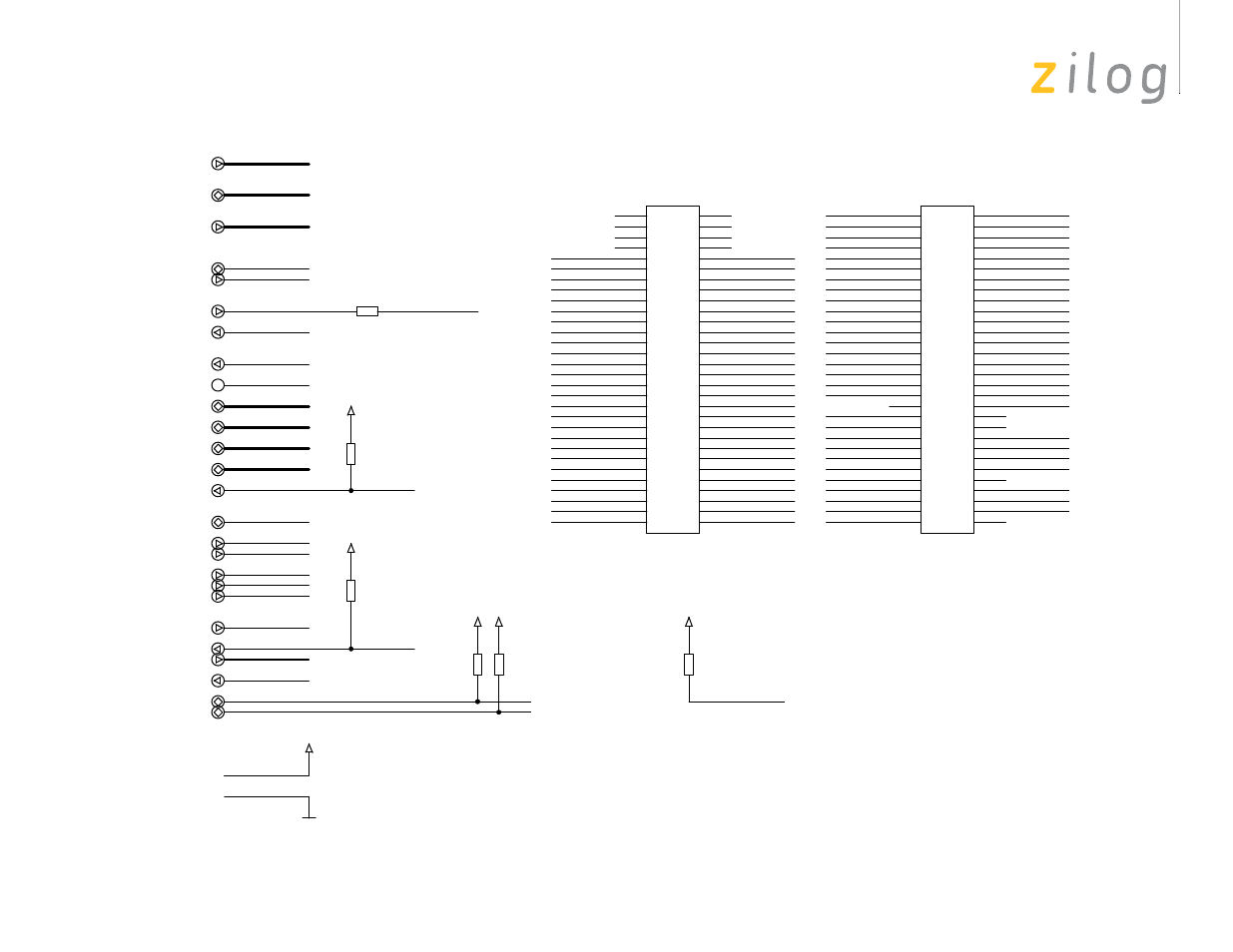

Figure 27. eZ80190 Module Schematic Diagram, #7 of 8—Headers

NC

( * WAI T * )

PB6

PB4

PB2

PB0

PC7

PC5

PC3

PC1

PD7

GND_EXT

PD4

PD2

PD0

ZDA

EZ80CLK

GND_EXT

NOTUSED1

GND_EXT

-NMI

A6

A10

GND_EXT

A8

A13

A15

A18

A19

A2

A11

A4

A5

-DIS_ETH

A21

A22

-CS0

-CS2

D1

D3

D5

D7

-MREQ

GND_EXT

-WR

-BUSACK

A0

A3

V3.3_EXT

A7

A9

A14

A16

GND_EXT

A1

A12

A20

A17

-DIS_FLASH

V3.3_EXT

A23

-CS1

D0

D2

D4

GND_EXT

D6

-IOREQ

-RD

-INSTRD

-BUSREQ

PB7

PB5

PB3

PB1

GND_EXT

PC6

PC4

PC2

PC0

PD6

PD5

PD3

PD1

GND_EXT

ZCL

RTC_VDD

IICSCL

IICSDA

-FLASHWE

-CS3

-RESET

V3.3_EXT

-HALT

GND_EXT

GND_EXT

V3.3_EXT

A[0..23]

D[0..7]

-CS[0..3]

PB[0..7]

PC[0..7]

PD[0..7]

CLK_OUT

RTC_VDD

EZ80CLK

-FLASHWE

IICSDA

IICSCL

-RD

-WR

-IOREQ

-INSTRD

NOTUSED1

-HALT

-BUSREQ

-BUSACK

-NMI

V3.3_EXT

ZDA

ZCL

GND_EXT

-MREQ

-DIS_FLASH

-RESET

-DIS_ETH

GND_EXT

V3.3_EXT

V3.3_EXT

GND_EXT

PA1

PA3

PA5

PA7

PA6

PA4

PA2

PA0

PA[0..7]

D[0..7]

A[0..23]

-CS[0..3]

PB[0..7]

PC[0..7]

PD[0..7]

-RESET

RTC_VDD

IICSDA

ZDA

ZCL

IICSCL

CLK_OUT

-RD

-WR

-IOREQ

-MREQ

-INSTRD

-BUSACK

-NMI

-DIS_ETH

-FLASHWE

-DIS_FLASH

-BUSREQ

-HALT

PA[0..7]

V3.3

GND

R24

33 0603

R28

10k

0603

R27

10k

0603

R29

10k

0603

R26

2k2

0603

R25

10k

0603

JP1

Header 30x2

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

JP2

Header 30x2

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

peripheral bus

connector

I/O connector

Pin 50 open,

to be keyed

place near eZ80

output (PHI)

connector 1

connector 2