Zilog EZ80190 User Manual

Page 73

UM014108-0810

Schematic Diagrams

eZ80190 Development Kit

User Manual

69

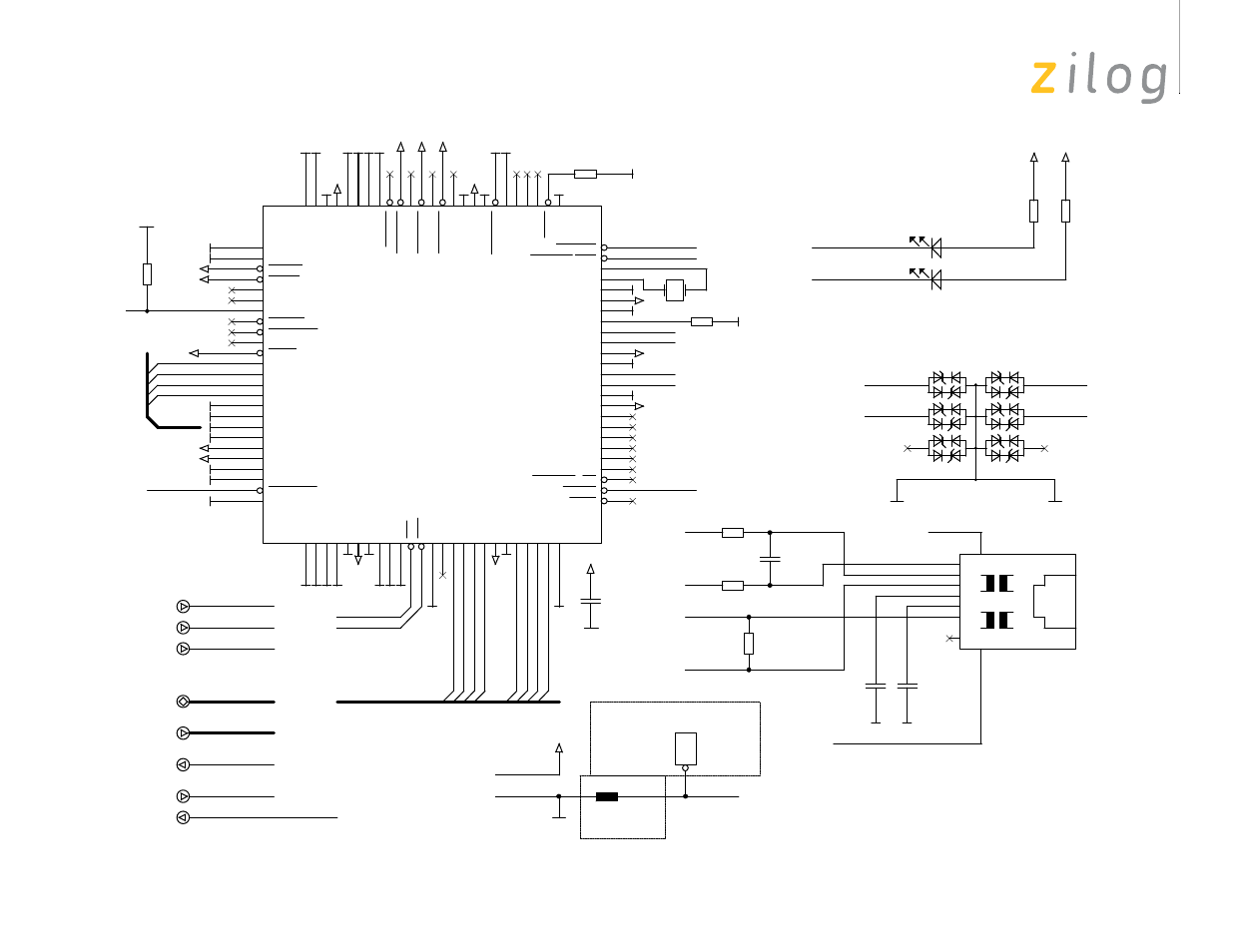

Figure 24. eZ80190 Module Schematic Diagram, #4 of 8—Ethernet Module

TX+ <- > 1

TX- <- > 2

RX+ <- > 3

RX- <- > 6

shi el d

=

i nt . Pul l - Up

lower LED

upper LED

-LANLED

RD+

RD-

TD+

TD-

-LINKLED

TD-

RXD-

RD-

TXD-

TXD+

RXD+

CTD

CRD

RD+

CASE

CASE

CASE

VSS

VDD

SD[0..7]

SA[0..3]

SD[0..7]

SA[0..3]

SD0

SD1 SD2

SD3

SD4 SD5

SD6 SD7

SA0

SA1

SA2

SA3

-DIS_ETH

RXD-

RXD+

TXD-

TXD+

ETHIRQ

ETHIRQ

-ETHWR

-ETHWR

-SLEEP

-LANLED

-ACTIVE

-SLEEP

-LANLED

-LINKLED

-ETHRD

-ETHRD

-DIS_ETH

TD+

SD[0..7]

SA[0..3]

-ETHRD

-ETHWR

-DIS_ETH

-SLEEP

ETHIRQ

-ACTIVE

GND

GND

V3.3

GND

LD1

5682F5;5

LED5682F

U8

LCDA15C-6

SO8.150

1

2

3

4

5

6

7

8

R9

100

0603

R10

100

0603

L1

ferrite

1210

JP4

HEADER 1

SIP1

1

U7

CS8900A-CQ3

TQFP100

71 72

73 74

65 66 67

68

58 59

60

51 52

53 54

37

1

38

2

39

3

40

4

41

5

42

6

43

7

44

8

45

9

46

10

47

11

48

12

49

13

50

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

55 56 57

61 62

63 64

69

70

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

SD4 SD5

SD6 SD7

SD0 SD1 SD2

SD3

SA17 SA18

SA19

SA13 SA14

SA15 SA16

SA0

A

VSS

SA1

ELCS

SA2

EECS

SA3

EESK

SA4

EEDA

T

AOUT

(TDO)

SA5

EEDA

T

AIN

SA6

CHIPSEL

SA7

DVSS

SA8

DVDD

SA9

DVSS

SA10

DMARQ2

SA11

DMACK2

REFRESH

DMARQ1

SA12

DMACK1

DMARQ0

DMACK0

CSOUT

SD15

SD14

SD13

SD12

DVDD

DVSS

SD1

1

SD10

SD9

SD8

MEMW

MEMR

INTRQ2

INTRQ1

INTRQ0

IOCS16

MEMCS16

INTRQ3

SHBE

DVSS DVDD DVSS

IOR IOW

AEN (TCK) IOCHRDY

DVDD

DVSS

RESET

TEST

SLEEP

BSTATU S/HC1

DI+

DI-

CI+

CI-

DO+

DO-

AVDD

AVSS

TXD+

TXD-

AVSS

AVDD

RXD+

RXD-

RES

AVSS

AVDD

AVSS

XTAL1

XTAL2

LINKLED/HC0

LANLED

R3

100

0603

Y1

20.000 MHz

HC49

R1

8R2

0603

R12

4k99/1%

0603

R2

8R2

0603

R11

4k7

0603

R8

10k

0603

C6

100nF

0603

C4

100nF

0603

C5

100nF

0603

J1

HFJ11-1041(E)

HALOFASTJACK

1

2

3

4

5

6

8

9

10

C3

560pF

0603

Dual-LED assembly,

right angle, grn/grn

do not stuff

do not

stuff

through-hole

solder pad

place near

FAST JACK

ESD protection array

green

green

device addresses:

00300h bis 0030Fh

plane or

big trace