Ez80190 module, D in the, Ez80190 module sch – Zilog EZ80190 User Manual

Page 70

UM014108-0810

Schematic Diagrams

eZ80190 Development Kit

User Manual

66

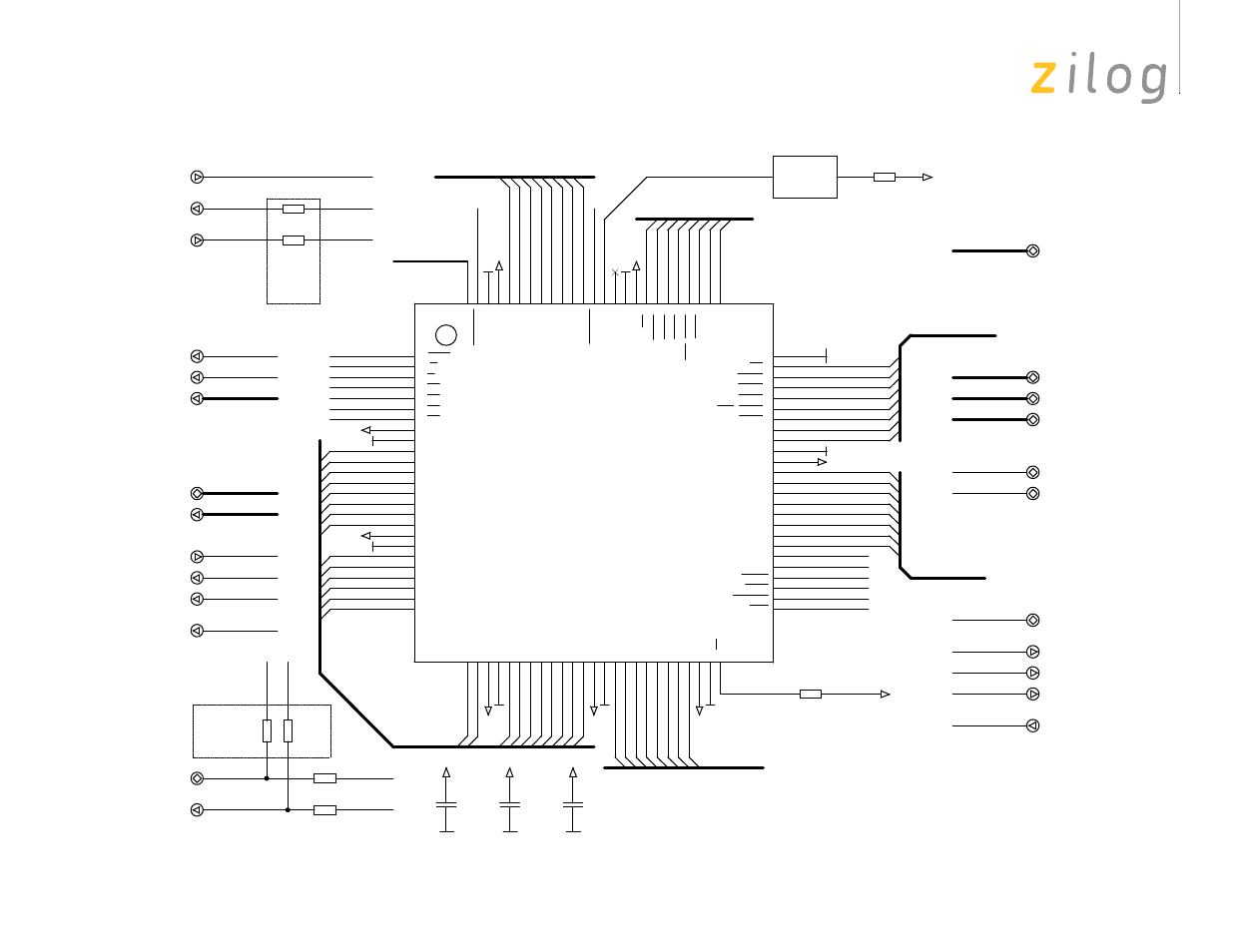

eZ80190 Module

Figures 21 through 28 present the schematics of the eZ80190 Module.

Figure 21. eZ80190 Module Schematic Diagram, #1 of 8—CPU

-CS0 --> FLASH

-CS1 --> RAM

-CS2 --> ext. IO

-CS3 --> ETH

=

don’t

stuff

place caps close

to pins 97, 8, 38, 48

don’t

stuff

PA[0..7]

D[0..7]

PC[0..7]

PB[0..7]

A[0..23]

D[0..7]

A[0..23]

PB[0..7]

D0 D1 D2

D3 D4

D5 D6 D7

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14 A15

A16 A17 A18

PA

0

PA

1

PA

2

PA

3

PA

4

PA

5

PA

6

PA

7

PD0

PD1

PD2

PD3

PC7

PC6

PC5

PC4

PC3

PC2

PC1

PC0

PB5

PB4

PB3

PB2

PB1

PB0

-CS0

-CS1

-CS2

-CS3

ZDA

ZCL

-BUSREQ

-RESET

PD6

PD7

PD4

PB7

PB6

-WR

-RD

-WR

-RD

ZDA

ZCL

-RESET

-SLEEP

-ACTIVE

CLK_OUT

CLK_OUT

A19 A20

A21 A22 A23

-CS[0..3]

-NMI

-IOREQ

-INSTRD

-HALT

-IOREQ

-INSTRD

-HALT

-MREQ

-BUSACK

PD5

XIN

PD[0..7]

PC[0..7]

PD[0..7]

-NMI

IICSDA

IICSCL

-BUSREQ

-BUSACK

-MREQ

PD7

PD6

PD4

ETHIRQ

PA7

PA6

PC1

PC0

PA[0..7]

D[0..7]

A[0..23]

-WR

-RD

ZDA

ZCL

-CS[0..3]

-RESET

-IOREQ

-INSTRD

-HALT

PB[0..7]

PC[0..7]

PD[0..7]

-NMI

ETHIRQ

-ACTIVE

-SLEEP

-BUSACK

-BUSREQ

-MREQ

CLK_OUT

IICSDA

IICSCL

PA[0..7]

C18

1nF

0603

C19

1nF

0603

C20

1nF

0603

U1

eZ80190

TQFP100

83

74

82

40

81

73

80

26

84

85

86

87

88

96

79

95

72

94

78

93

75

97

98

99

100

92

77

91

4

90

76

89

71

5

70

41

27

69

42

68

6

67

1

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

30

43

7

44

31

2

32

45

33

3

28

34

29

46

35

8

36

47

37

9

10

38

11

39

12

13

14

48 49

15

50

16

17

18

19

20

21

22

23

24

25

PD7/RI0

PC7/RI1

PD6/DCD0

D0

PD5/DSR0

PC6/DCD1

PD4/DTR0

A14

VDD

VSS

XT

AL

EXT

AL

BUSACK

PA

7

PD3/SS0/CTS0

PA

6

PC5/DSR1

PA

5

PD2/SCK0/R

TS0

PA

4

TEST

VDD

VSS

BUSREQ

PHI

PA

3

PD1/SDA0/MOSI0/RxD0

PA

2

CS0

PA

1

PD0/SCL0/MISO0/TxD0

PA

0

PC4/DTR1

CS1

PC3/SS1/CTS1

D1

A15

PC2/SCK1/RTS1

D2

PC1/SDA1/MOSI1/RxD1

CS2

PC0/SCL1/MISO1/TxD1

MREQ

HALT

INSTRD

IORQ

RESET

ZCL

ZDA

PB0

PB1

PB2

PB3

PB4

PB5

PB6

PB7

VDD

VSS

A16

D3

CS3

D4

A17

WR

A18

D5

A19

RD

VDD

A20

VSS

D6

A21

VDD

A22

D7

A23

VSS

A0

VDD

A1

VSS

A2

A3

A4

VDD VSS

A5

NMI

A6

A7

VDD

VSS

A8

A9

A10

A11

A12

A13

R4

1k

0603

R32

0R

0603

R33

0R

0603

R31

0R

0603

R30

0R

0603

R14

0R

0603

X1

50.000MHz, 3.3V

SG-710

1

3

OE

OUT

R13

4k7

0603

R15

0R

0603