Endat, biss, hiperface dsl encoder interface, Resolver sine and cosine encoder interface – Altera Multiaxis Motor Control Board User Manual

Page 12

Page 12

Functional Description

Multiaxis Motor Control Board

February 2014

Altera Corporation

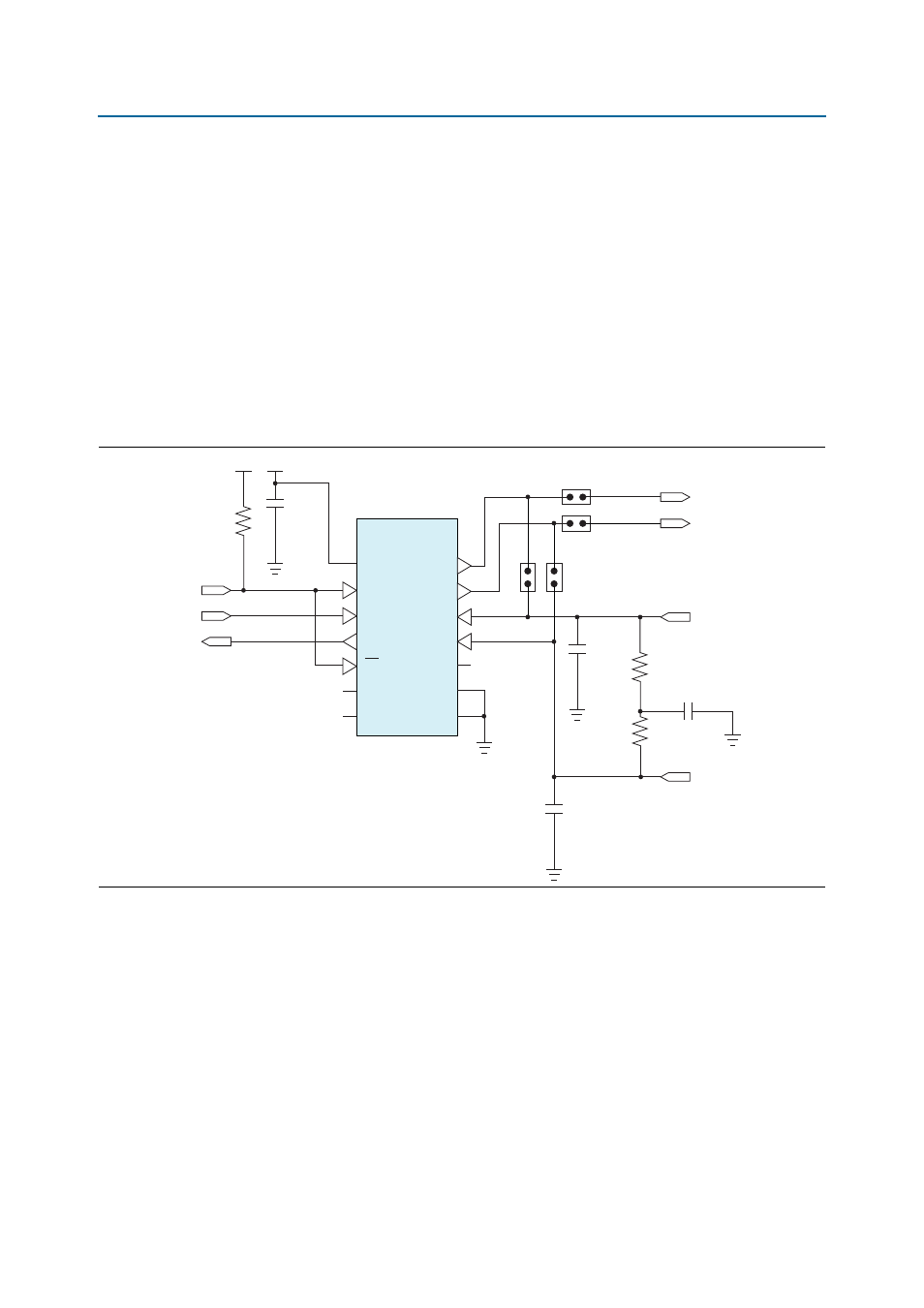

EnDat, BiSS, HIPERFACE DSL Encoder Interface

The Multiaxis Motor Control Board supports connection of encoders with RS485

interfaces. You may configure each motor channel independently for any of the

encoder interface types.

Each encoder interface type requires you to implement the appropriate interface IP

cores in the FPGA on the host board. Altera partners provide appropriate IP cores

with the reference design.

The Multiaxis Motor Control Board includes different electrical termination schemes

for the encoder interfaces.

shows an example a channel (channel 0) interface

termination. Capacitors C107 and C111 are not fitted, Resistors R103, R106 and

capacitor C109 are fitted. The jumpers allow for independent pairs for TX and RX or

one common pair. Refer to

Table 11

for other channel jumper settings.

Resolver Sine and Cosine Encoder Interface

The FPGA on the host board implements IP cores to drive the single-ended resolver

stimulus signal with a sigma-delta encoded 8-kHz sine wave. The Multiaxis Motor

Control Board converts and filters this signal to a differential drive for the resolver.

ADS1205 dual channel 10-MHz sigma-delta ADCs, with a ±2.5-V input range, clocked

at 20 MHz, digitize resolver encoder sine and cosine feedback signals. The ADS1205

divides the applied clock internally to generate the 10-Mbps data rate. The Multiaxis

Motor Control Board passes the resulting bitstreams through isolators for isolation.

Figure 8. Encoder Interface Termination

VDD

DE

D

R

RE

NC1

NC2

Y

Z

A

B

NC3

GND1

GND2

+5 V

J5

J6

J7

J8

DRV_0_RS485_EN

DRV_0_RS485_TX

DRV_0_RS485_RX

+5 V

DRV_0_SER_DATA_TX_P

DRV_0_SER_DATA_TX_N

DRV_0_SER_DATA_RX_P

DRV_0_SER_DATA_RX_N

LTC1687CS

DNP

330 pF

200 V

DNP

330 pF

200 V

56 R

56 R

4K7

16 V

0.1

µF

16 V

2.2

µF