Altera Temperature Sensor User Manual

Page 7

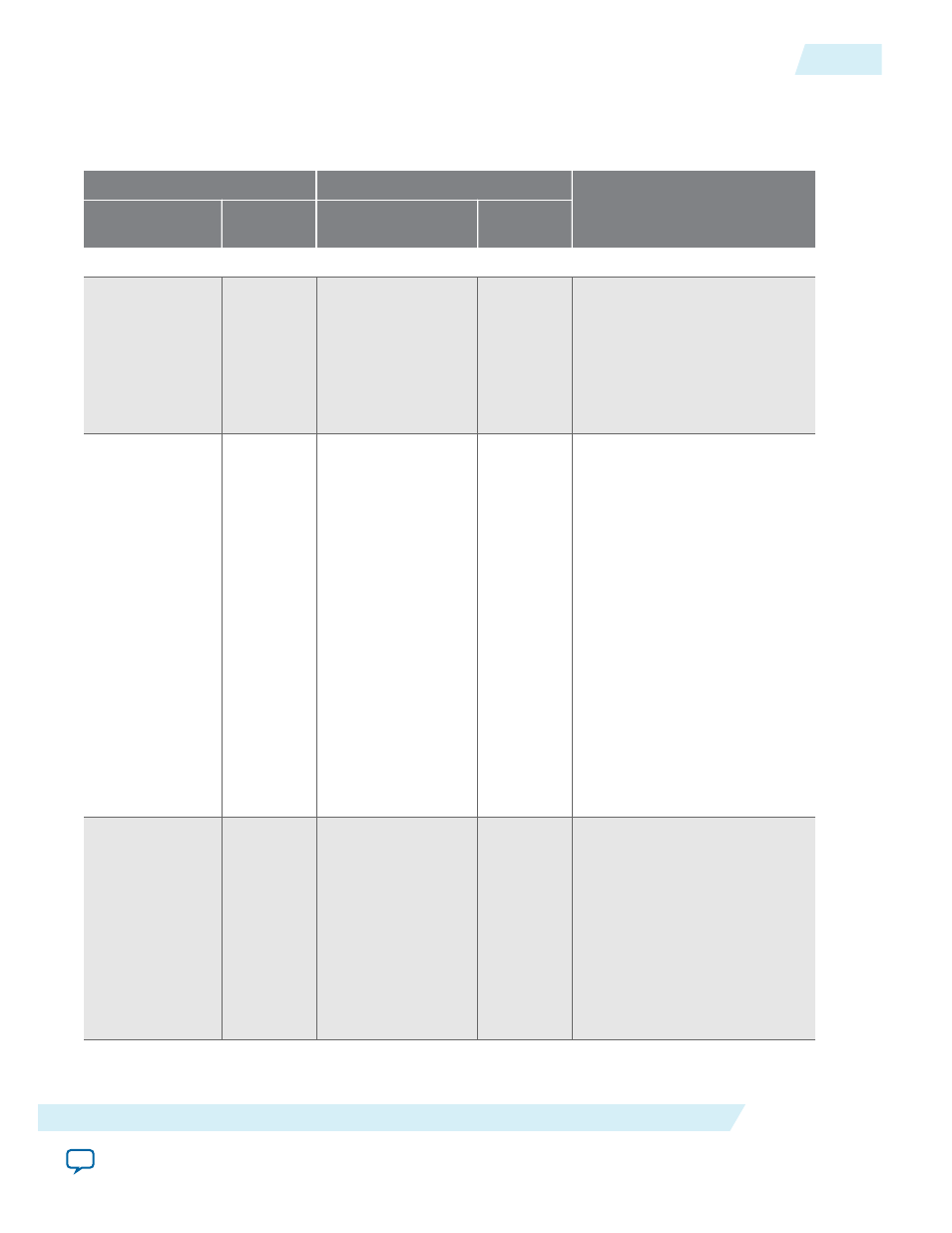

This table lists the parameter editor and CLI parameter settings for the Altera Temperature Sensor IP

core.

Table 3: Altera Temperature Sensor IP core Parameter Settings

Parameter

CLI Parameter

Description

Name

Legal

Values

Name

Legal

Values

General Options Tab

What is the

input

frequency?

1.0 – 80.0

MHz

clk_frequency

1.0 – 80.0

Specifies the input frequency

of the

clk

signal. The input

frequency value is type string,

and the value must be less

than or equal to the clock

divider value.

The default value is 1.0

What is the

clock divider

value?

40, 80

clock_divider_value

40, 80

Specifies the clock divider

value. The IP core divides the

clock frequency value with the

clock divider value before

feeding the ADC. This option

is only enabled when the

clk

signal frequency is more than

1 MHz.

Altera recommends clocking

the ADC with a 500 kHz

signal.

The CLI parameter is type

integer. Ensure that you

enable the clock divider by

setting the

clock_divider_

enable

parameter value to

on.

The default value is 40.

Create a clock

enable port

On/Off

ce

—

Specifies whether to turn on

the asynchronous clock enable

(

ce

) port.

Turn on this option when you

want to enable the Altera

Temperature Sensor IP core.

When you turn off this

option, the clock enable port

automatically connects to

VCC.

UG-01074

2015.05.04

Altera Temperature Sensor Parameters

7

Altera Temperature Sensor IP Core User Guide

Altera Corporation