General i/o power, Figure 3–14, Shows – Altera PowerPlay Early Power Estimator User Manual

Page 33

Altera Corporation

3–17

October 2005

PowerPlay Early Power Estimator User Guide: Stratix, Stratix GX & Cyclone FPGAs

Using PowerPlay Early Power Estimator for Stratix, Stratix GX & Cyclone FPGAs

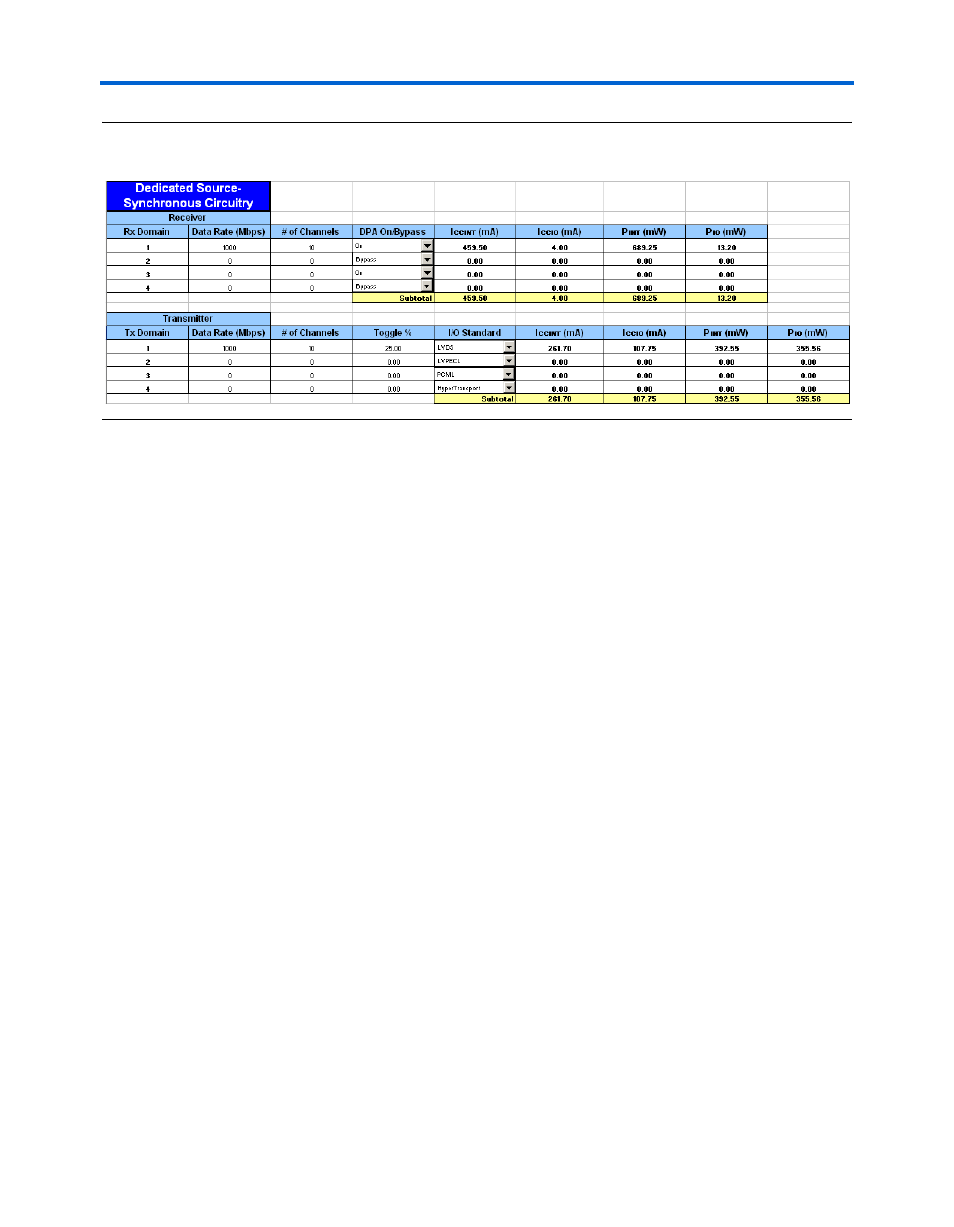

Figure 3–14. Dedicated Source-Synchronous Circuitry Section in the Stratix GX PowerPlay Early Power

Estimator

General I/O Power

Stratix, Stratix GX, and Cyclone devices feature programmable I/O pins

that support a wide range of industry I/O standards, permitting

increased design flexibility. The General I/O Power section in the

PowerPlay early power estimator enables you to estimate the I/O pin

power consumption based on their I/O standards.

1

For I/O standards that recommend termination resistors (for

example, SSTL and HSTL), the PowerPlay early power

estimator assumes you are using external termination resistors.

The I

CC

and power reported is for external termination. If you are not

using external termination resistors, you should choose the LVTTL I/O

standard with the same V

CCIO

and similar drive strength as the

terminated I/O standard. For example, if you are using SSTL-2 class II

and are only doing a point-to-point connection and are not using

termination resistors, you should select 2.5_LVTTL/LVCMOS_16 as

your I/O standard.

The current consumed by the V

REF

pins is minimal (less than 10

μA).

Therefore, this information is not included in the PowerPlay early power

estimator, since it s negligible when compared to the power consumed by

the general-purpose I/O pins.

Each row in the General I/O Power section represents a design module

where the I/O pins have the same frequency, toggle percentage, average

capacitive load, I/O standard, and data rate. Enter the clock frequency

(f

MAX

) in MHz, the number of output and bidirectional pins with this

configuration, toggle percentage of the pins, the average capacitance of