Altera PowerPlay Early Power Estimator User Manual

Page 24

3–12

Chapter 3: Using Cyclone III PowerPlay Early Power Estimator

PowerPlay Early Power Estimator Inputs

PowerPlay Early Power Estimator User Guide for Cyclone III FPGAs

© June 2009 Altera Corporation

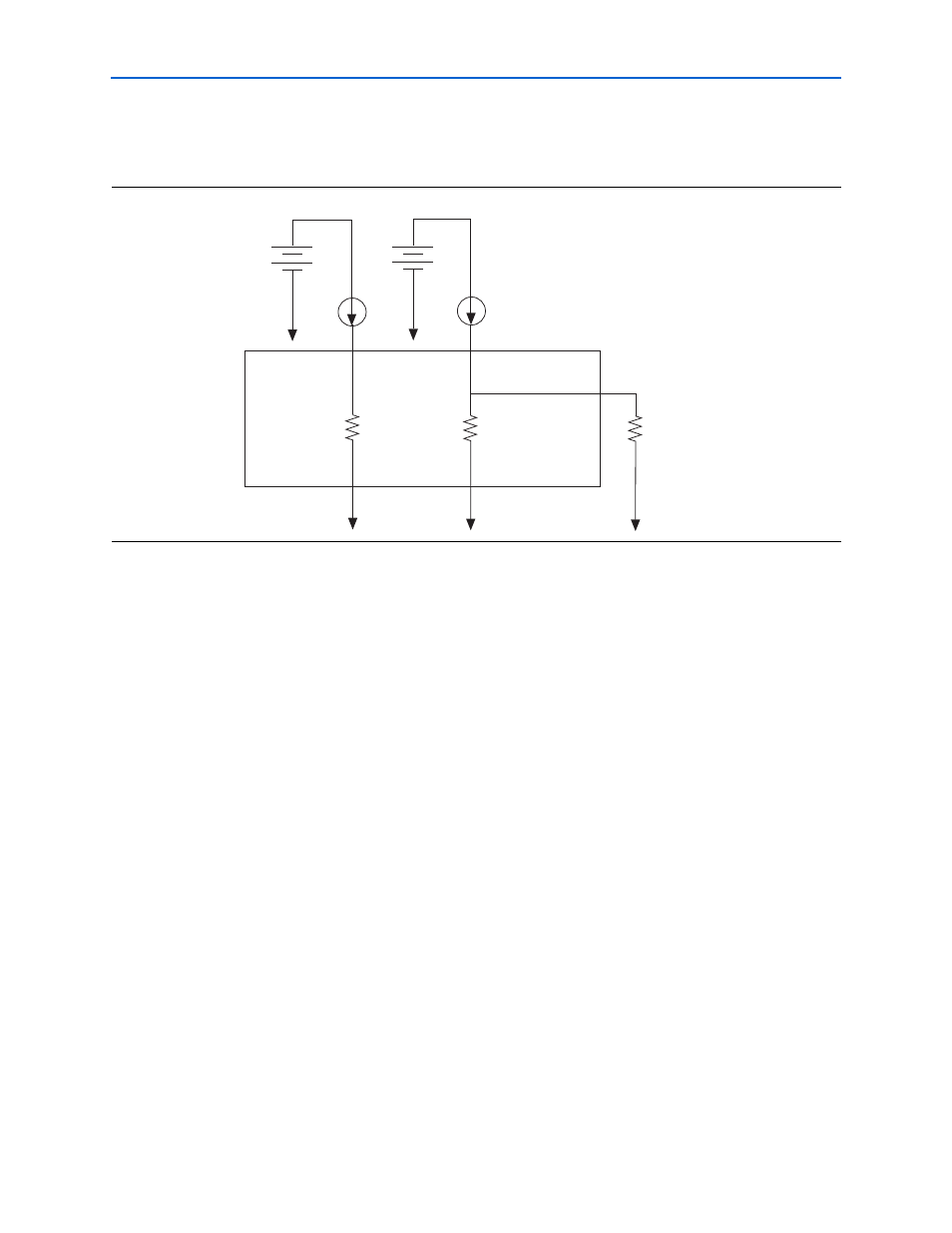

Figure 3–7

shows a graphical representation of the I/O power consumption. The I

CCIO

rail power includes both the thermal P

IO

and external P

IO

.

V

REF

pins consume minimal current (less than 10 A) that is negligible when

compared to the power consumed by the general purpose I/O pins. Therefore, the

PowerPlay Early Power Estimator does not include the current for V

REF

pins in the

calculations.

Each row in the I/O section represents a design module where the I/O pins have the

same I/O standard, current strength or output termination, data rate, clock frequency,

output enable static probability, and capacitive load. You must enter the following

parameters for each design module:

■

I/O standard

■

Current Strength/Output Termination

■

Number of input, output, and bidirectional pins

■

I/O data rate

■

Clock frequency (f

MAX

) in MHz

■

Average pin toggle percentage

■

Output enable static probability

■

Capacitance of the load

Figure 3–7. I/O Power Representation

Cyclone III Device

I

CCINT

I

CCIO

V

CCINT

V

CCIO

Thermal P

INT

Thermal P

IO

External P

IO