Nco ip core performance and resource utilization – Altera NCO MegaCore Function User Manual

Page 7

Altera verifies that the current version of the Quartus II software compiles the previous version of each IP

core. Altera does not verify that the Quartus II software compiles IP core versions older than the previous

version. The Altera IP Release Notes lists any exceptions.

Related Information

•

•

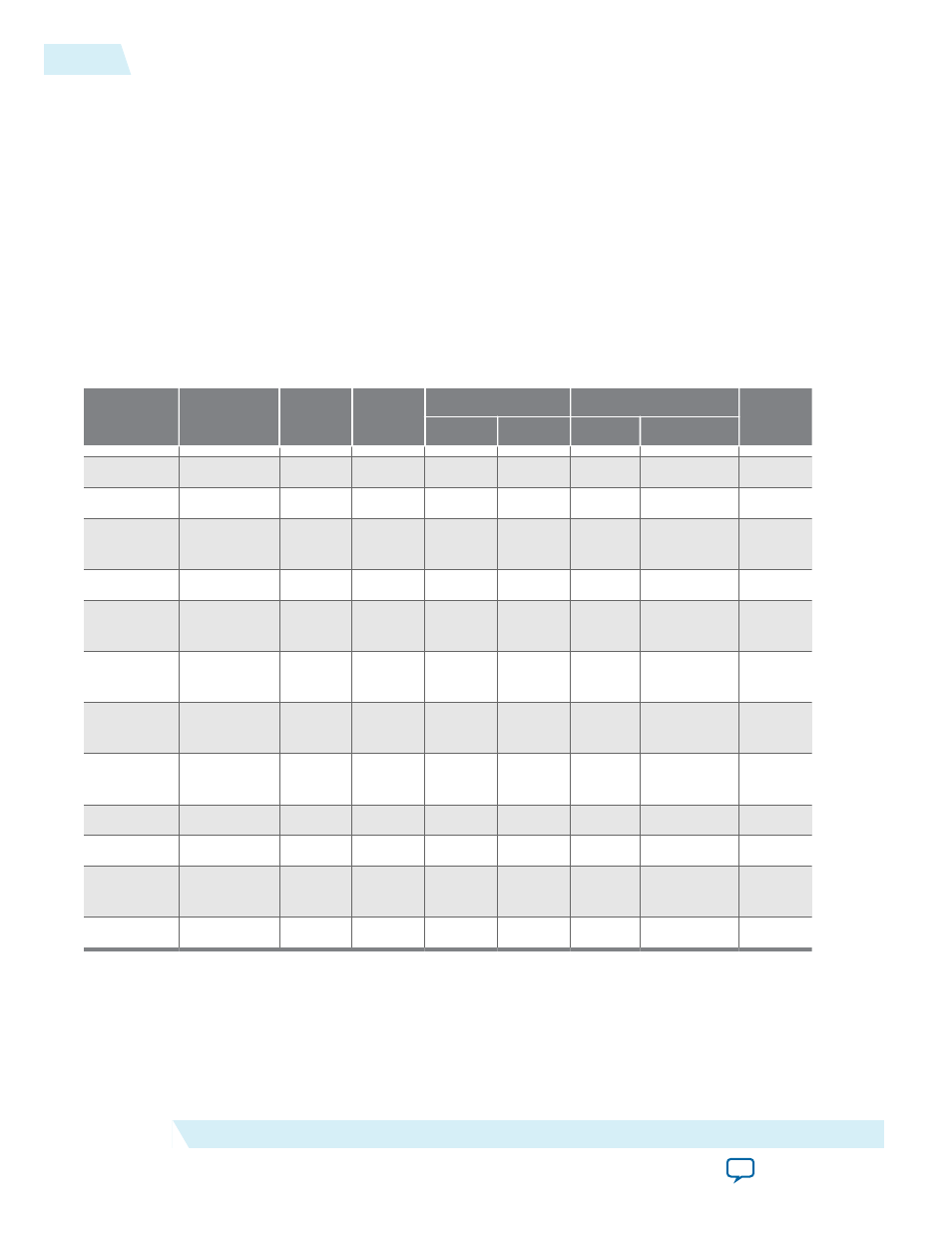

NCO IP Core Performance and Resource Utilization

Table 1-3: NCO IP Core Performance

Typical performance using the Quartus II software with the Arria V (5AGXFB3H4F40C4), Cyclone V

(5CGXFC7D6F31C6), and Stratix V (5SGSMD4H2F35C2) devices

Device

Parameters

ALM

DSP

Blocks

Memory

Registers

f

MAX

(MHz)

M10K

M20K

Primary

Secondary

Arria V Cordic

838

0

1

--

1,879

8

340

Arria V Large Rom

56

0

12

--

149

0

350

Arria V Multiplier

Based

92

2

2

--

244

2

310

Arria V Small ROM 132

0

6

--

300

0

350

Cyclone

V

Cordic

838

0

1

--

1,881

6

260

Cyclone

V

Large Rom

56

0

12

--

149

0

275

Cyclone

V

Multiplier

Based

92

2

2

--

244

2

275

Cyclone

V

Small ROM 120

0

6

--

300

0

275

Stratix V Cordic

838

0

--

1

1,881

6

644

Stratix V Large Rom

56

0

--

5

149

0

700

Stratix V Multiplier

Based

92

2

--

2

245

1

500

Stratix V Small ROM 126

0

--

3

300

0

700

1-4

NCO IP Core Performance and Resource Utilization

UG-NCO

2014.12.15

Altera Corporation

About the NCO IP Core