Altera NCO MegaCore Function User Manual

Page 33

To meet the specification, the design uses the following parameters:

• Multiplier-based algorithm. By using the dedicated multiplier circuitry in Stratix devices, the NCO

architectures that implement this algorithm can provide very high performance.

• Clock rate of 200 MHz and 32-bit phase accumulator precision to give a frequency resolution of 47

mHz.

• Angular and magnitude precision settings give an SFDR of approximately 100.05 dB to meet the SFDR

requirement, while minimizing the required device resources. s.

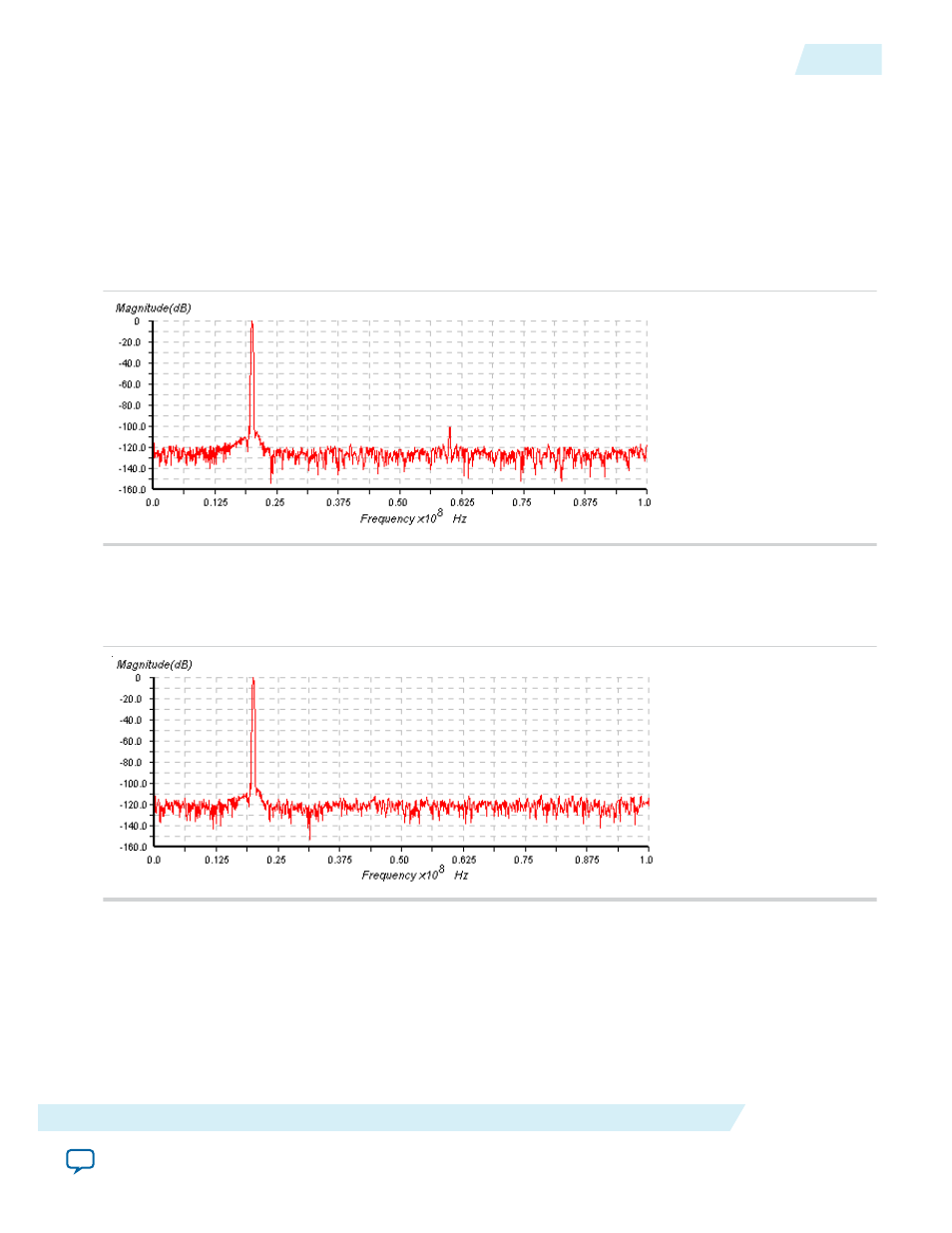

Figure 4-3: Spectrum After Setting Angular and Magnitude PrecisionAngular precision = 17 bits;

magnitude precision = 18 bits

• Dither level to increase the variance of the dithering sequence until the design reaches the trade-off

point between spur reduction and noise level augmentation. At a dithering level of 3, the SFDR is

approximately 110.22 dB, which exceeds the specification.

Figure 4-4: Spectrum After the Addition of Dithering

• The frequency modulation input allows an external frequency for modulating the input signal. The

modulator resolution is 32 bits and the modulator pipeline level is 1.

• A phase modulation input, which is necessary with 32 bits for modulator precision and the modulator

pipeline level is 1.

• Dual output for generating both the sine and cosine outputs.

• Four multichannels.

Simulation Specification

UG-NCO

2014.12.15

NCO Design Example Specification

4-3

NCO Multichannel Design Example

Altera Corporation