Multiplier-based architecture, Multiplier-based architecture -4 – Altera NCO MegaCore Function User Manual

Page 21

only. Therefore, the algorithm can be implemented efficiently by a series of simple binary shift and

additions/subtractions.

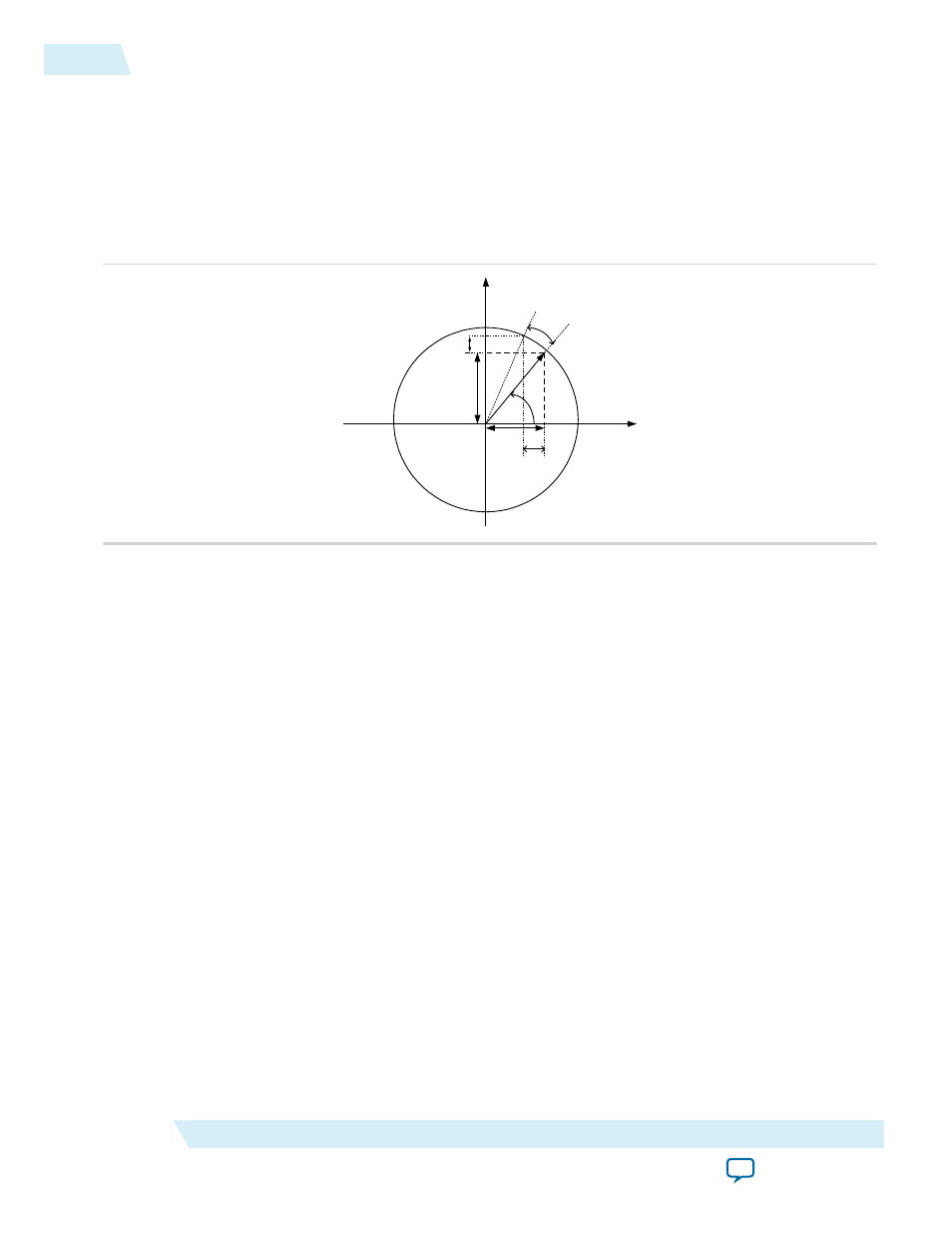

In an NCO, the CORDIC algorithm computes the sine and cosine of an input phase value by iteratively

shifting the phase angle to approximate the cartesian coordinate values for the input angle. At the end of

the CORDIC iteration, the x and y coordinates for a given angle represent the cosine and sine of that

angle, respectively.

Figure 3-3: CORDIC Rotation for Sine & Cosine Calculation

ø

sin ø

cos ø

y

x

dø

dx

dy

With the NCO MegaCore function, you can select parallel (unrolled) or serial (iterative) CORDIC

architectures:

• You an use the parallel CORDIC architecture to create a very high-performance, high-precision

oscillator—implemented entirely in logic elements—with a throughput of one output sample per clock

cycle. With this architecture, there is a new output value every clock cycle.

• The serial CORDIC architecture uses fewer resources than the parallel CORDIC architecture.

However, its throughput is reduced by a factor equal to the magnitude precision. For example, if you

select a magnitude precision of N bits in the NCO MegaCore function, the output sample rate and the

Nyquist frequency is reduced by a factor of N. This architecture is implemented entirely in logic

elements and is useful if your design requires low frequency, high precision waveforms. With this

architecture, the adder stages are stored internally and a new output value is produced every N clock

cycles.

Multiplier-Based Architecture

The multiplier-based architecture uses multipliers to reduce memory usage. You can choose to implement

the multipliers in either:

• Logic elements (Cyclone series) or combinational ALUTs (Stratix series).

• Dedicated multiplier circuitry (for example, dedicated DSP blocks) (Stratix or Arria series).

Note: When you specify a dual output multiplier-based NCO, the IP core provides an option to output a

sample every two clock cycles. This setting reduces the throughput by a factor of two and halves the

resources required by the waveform generation unit.

3-4

Multiplier-Based Architecture

UG-NCO

2014.12.15

Altera Corporation

NCO IP Core Functional Description