Altera I/O Buffer (ALTIOBUF) IP Core User Manual

Page 17

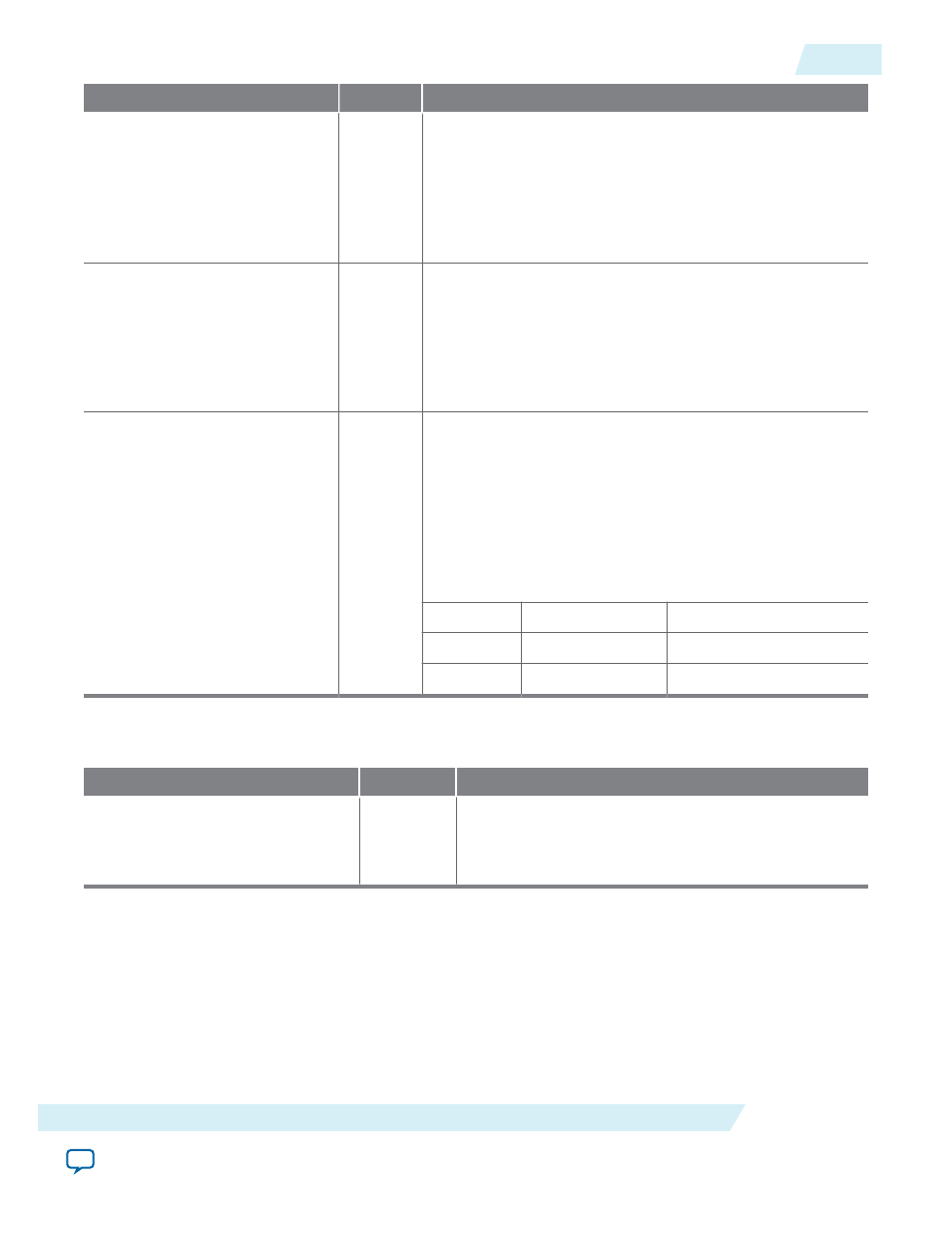

Name

Required

Description

io_config_clkena[]

No

Input clock-enable that feeds the ena port of

IO_CONFIG

for

user-driven dynamic delay chain.

Input port

[NUMBER_OF_CHANNELS - 1..0]

wide. Input

port used as the clock enable signal of the shift register

block. This port is available only if the

USE_IN_DYNAMIC_

DELAY_CHAIN

parameter value is

TRUE.

io_config_update

No

Input port that feeds the

IO_CONFIG

update port for user-

driven dynamic delay chain.

When asserted, the serial load shift register bits feed the

parallel load register. The value is a 1-bit wire shared among

all I/O instances. This port is available only if the

USE_IN_

DYNAMIC_DELAY_CHAIN

parameter value is TRUE.

dynamicterminationcon-

trol[]

No

Input signal for bidirectional I/Os.

Input port

[NUMBER_OF_CHANNELS - 1..0]

wide. When

specified, this port selects from the core either

Rs

code,

when the input value is

LOW

; or

Rt

code, when the input

value is

HIGH

. Enable

Rt

only when the bidirectional I/O is

receiving input. When the bidirectional I/O is not receiving

input, disable this port for optimal output performance and

power dissipation.

Value

Rs Code

Rt Code

0

1

0

1

0

1

Table 7: ALTIOBUF (As Input Buffer) Output Ports

This table shows the output ports for the ALTIOBUF IP core (as input buffer).

Name

Required

Description

dataout[]

Yes

Input buffer output port.

Input port

[NUMBER_OF_CHANNELS - 1..0]

wide. The

I/O input buffer element output.

UG-01024

2014.12.15

ALTIOBUF Signals and Parameters: As Input Buffer

17

I/O Buffer (ALTIOBUF) IP Core User Guide

Altera Corporation