File locations, Demonstration setup – Altera Cyclone II FPGA Starter User Manual

Page 48

6–6

Altera Corporation

Cyclone II FPGA Starter Development Kit User Guide

October 2006

SD Card Music Player

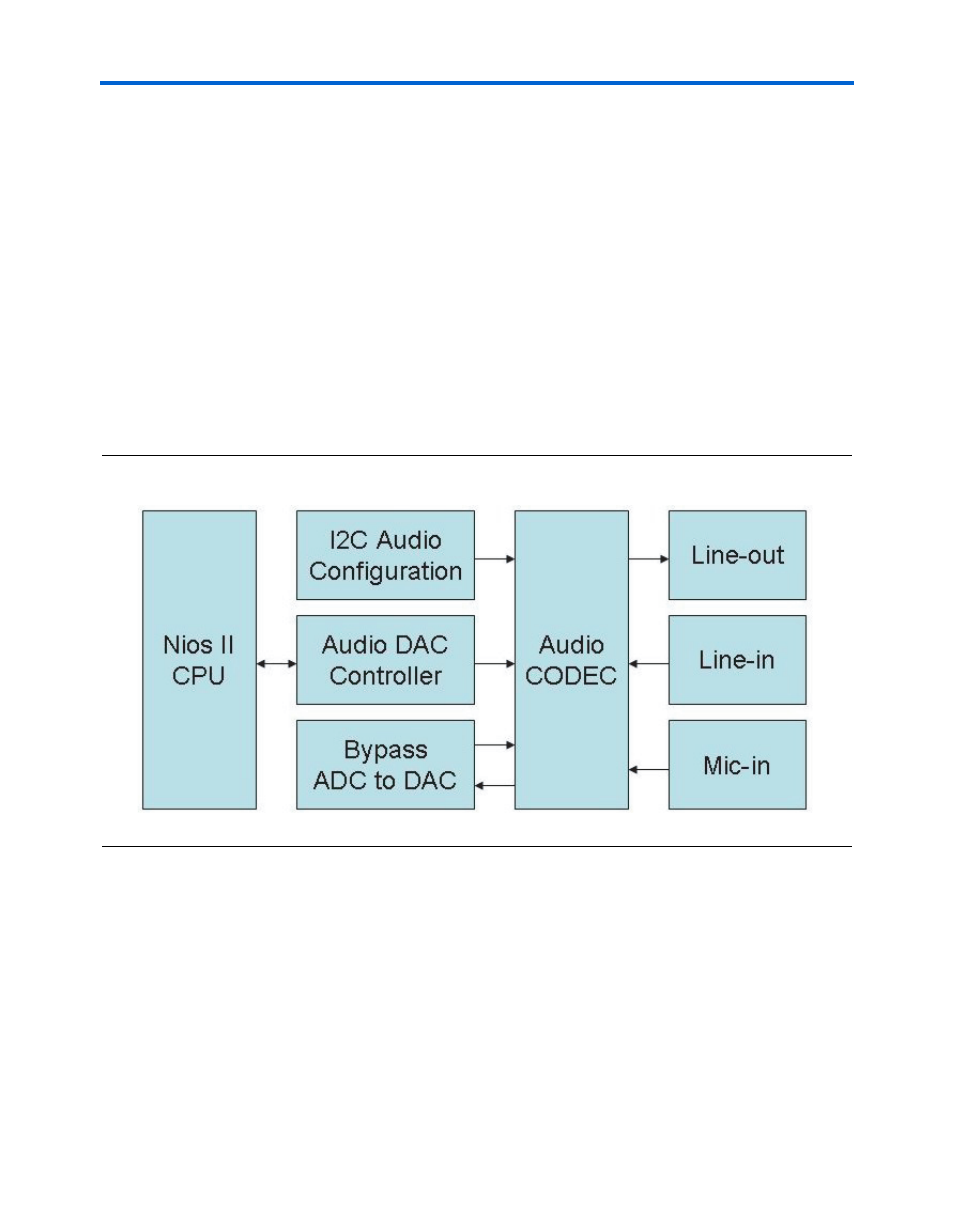

Because the audio CODEC is configured in the slave mode, external

circuitry must provide the ADC/DAC serial bit clock (BCK) and left/right

channel clock (LRCK) to the audio CODEC. The block diagram

(

) shows that the sample design provides an audio DAC

controller for clock generation and data flow control. The audio DAC

controller is integrated into the Avalon bus architecture, so that the

Nios II processor can control the application.

During operation, the Nios II processor checks if the FIFO memory of the

audio DAC controller becomes full. If the FIFO is not full, the processor

reads a 512-byte sector and sends the data to the FIFO of the audio DAC

controller via the Avalon bus. The audio DAC controller uses a 48 kHz

sample rate to send the data and clock signals to the audio CODEC. The

design also mixes the data from the Mic In port with data from the Line

In

port for the Karaoke-style effects.

Figure 6–3. SD Music Player Block Diagram

File Locations

■

Project directory: CII_Starter_SD_Card_Audio

■

Bit stream used: CII_Starter_SD_Card_Audio.sof (or .pof)

■

Nios II Workspace: CII_Starter_SD_Card_Audio

Demonstration Setup

To set up the demonstration, perform the following steps: