Controlling the 7-segment displays, Controlling the 7-segment displays –2 – Altera Cyclone II FPGA Starter User Manual

Page 24

4–2

Altera Corporation

Cyclone II FPGA Starter Development Kit User Guide

October 2006

Controlling the 7-Segment Displays

■

Configure user ports

■

Load music to memory and play music via the audio digital analog

converter (DAC) output

■

Load an image pattern for VGA output

The following sections describe how to perform these actions with the

Control Panel already open on the host computer. If not already open,

launch the Control Panel as described in

Controlling the

7-Segment

Displays

Typical design activities do not require the ability to set arbitrary values

into simple display devices. However, used for troubleshooting, this

ability enables the user to verify that these devices operate correctly.

To set the value of a 7-segment module to display, perform the following

steps:

1.

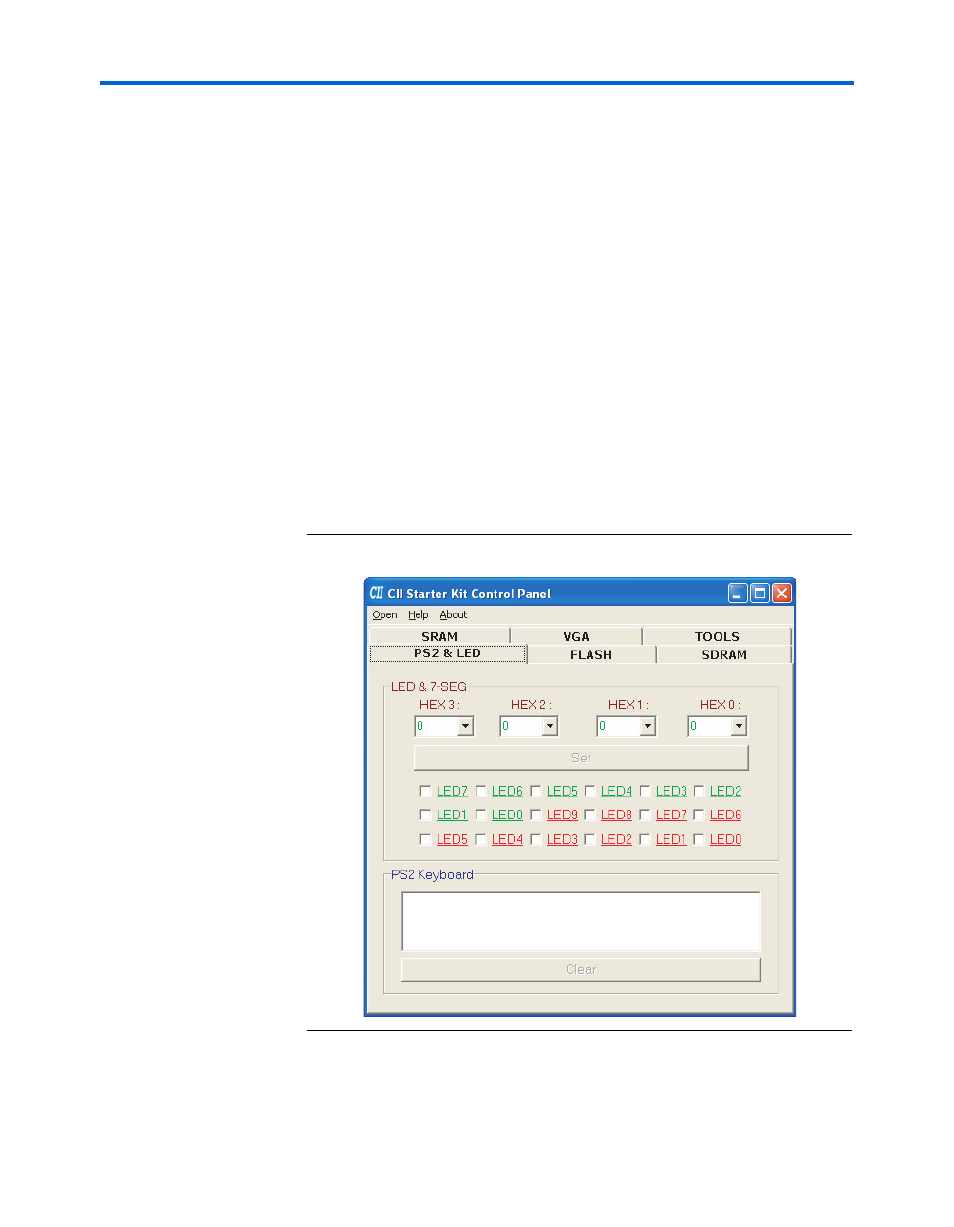

Select the PS2 & LED tab on the Control Panel (

).

Figure 4–2. Control Panel Window for 7-Segment Controls

2.

In the LED & 7-SEG area, enter a value for any of the 7-segment

modules labeled HEX0 through HEX3.