Altera Clock Control Block IP Core User Manual

Page 9

Chapter 2: Parameter Settings

2–3

MegaWizard Parameter Settings

February 2014

Altera Corporation

Clock Control Block (ALTCLKCTRL) Megafunction

User Guide

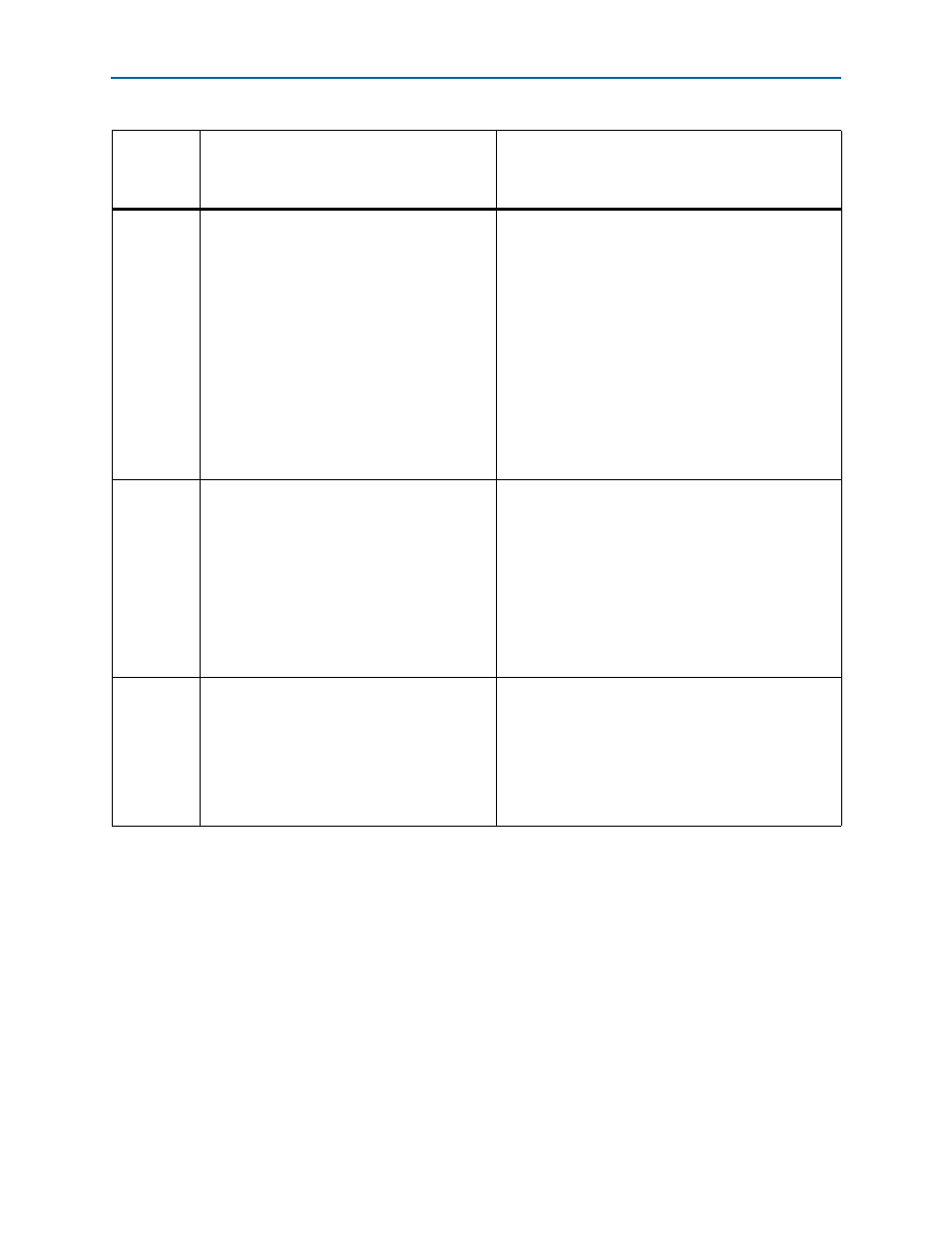

How do you want to register the 'ena' port?

Turn on this option to choose the register mode for cthe

ena

port. The available register modes are:

Falling edge of input clock—the clkout pin is the

output of the first falling edge driven register.

Double register with input clock—the clkout pin is

the output of the second falling edge driven register.

Not registered—the clkout pin is set to one of the

clkin

input (after the multiplexer).

This option is available after you turn on the Create ‘ena’

port to enable or disable the clock network driven by

this buffer option.

This option is available in Stratix III, Stratix IV, and Stratix

V devices only.

3

Ensure glitch-free switchover implementation

Turn on this option to implement a glitch-free switchover

when you use multiple clock inputs.

You must ensure the clock that is currently selected is

running before switching to another source. If the

selected clock is not running, the glitch-free switchover

implementation will not be able to switch to the new

clock source.

By default, the clkselect port is set to 00. A clock must

be applied to inclk0x for the values on the clkselect

ports to be read.

4

Generate netlist

Turn on this option if you want to generate a netlist for

your third-party EDA synthesis tool to estimate the timing

and resource usage of the megafunction. If you turn on

this option, a netlist file (_syn.v) is generated. This file is

a representation of the customized logic used in the

Quartus II software and provides connectivity of the

architectural elements in the megafunction but may not

represent true functionality.

Table 2–1. ALTCLKCTRL MegaWizard Plug-In Manager Page Options and Description (Part 3 of 4)

MegaWizard

Plug-in

Manager

Page

Configuration Setting

Description