Global clock control block, Global clock control block –2, Global – Altera Clock Control Block IP Core User Manual

Page 14

3–2

Chapter 3: Functional Description

Clock Control Block

Clock Control Block (ALTCLKCTRL) Megafunction

February 2014

Altera Corporation

User Guide

1

You must ensure the clock that is currently selected is running before switching to

another source. If the selected clock is not running, the glitch-free switchover

implementation will not be able to switch to the new clock source.

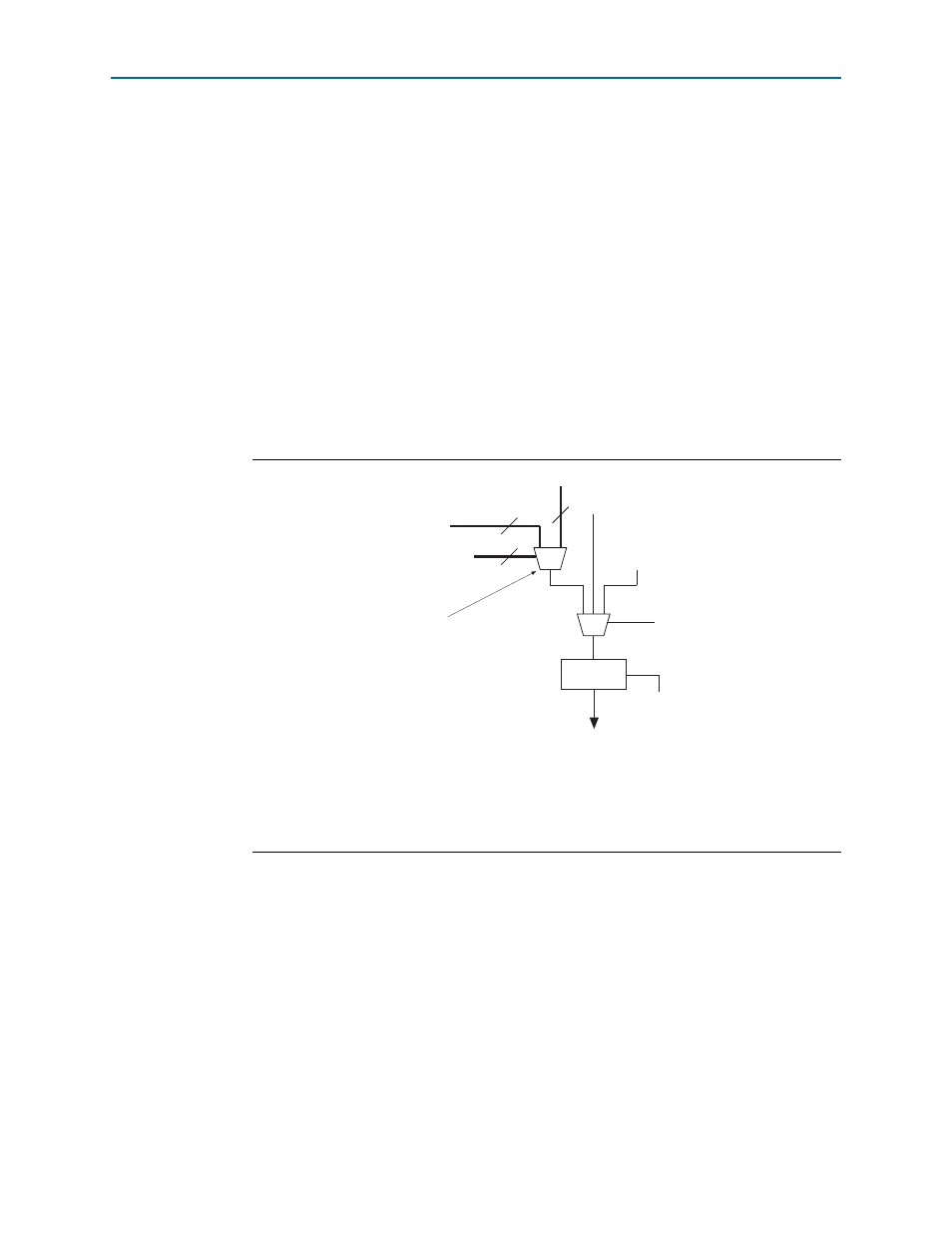

Global Clock Control Block

When a clock control block is configured to drive a global clock network, you can

select the clock source statically or you can control the selection dynamically by using

internal logic to drive multiplexer selector inputs. When selecting the clock source

statically, you can set the clock source to any of the inputs. For example, you can use

the dedicated CLK pin, internal logic, and PLL outputs.

When selecting the clock source dynamically, you can select two PLL outputs (such as

c0

or c1), a combination of clock pins, or PLL outputs.

Figure 3–1

shows a clock control block and the possible sources that can drive the

global clock network.

f

For more information about global clock control block or network in a specific device,

refer to the respective device handbook.

Figure 3–1. Global Clock Control Block

Notes to

Figure 3–1

:

(1) You can dynamically control these clock select signals through internal logic only when the device is operating in user

mode.

(2) You can only set these clock select signals through a configuration file and cannot be dynamically controlled during

user-mode operation.

2

2

2

GCLK

Internal Logic

Internal Logic

CLKn Pin

CLKp Pin

PLL Counter Outputs

CLKSELECT [1..0]

(1)

Enable/

Disable

Static Clock Select

(2)

This multiplexer

supports user-controlled

dynamic switching.