System requirements – Altera DDR3 SDRAM High-Performance Controller and ALTMEMPHY IP User Manual

Page 8

15–8

Chapter 15: Introduction to ALTMEMPHY IP

System Requirements

External Memory Interface Handbook

November 2012

Altera Corporation

Volume 3: Reference Material

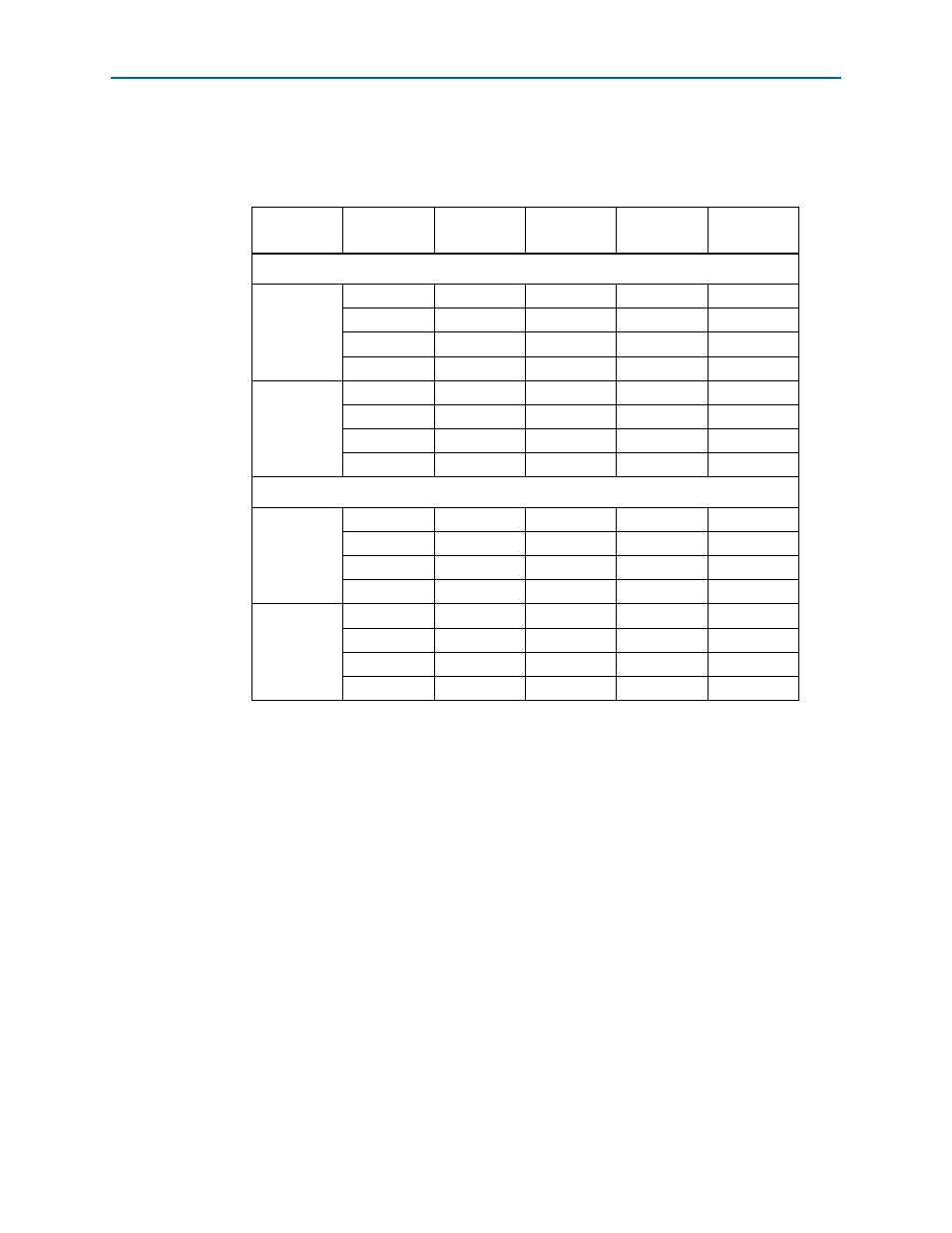

shows resource utilization data for the DDR2 high-performance controller

and controller plus PHY, for half-rate and full-rate configurations for Cyclone III

devices.

System Requirements

The DDR3 SDRAM Controller with ALTMEMPHY IP is a part of the MegaCore IP

Library, which is distributed with the Quartus II software and downloadable from the

Altera

website,

f

For system requirements and installation instructions, refer to

.

Table 15–9. DDR2 Resource Utilization in Cyclone III Devices

Protocol

Memory

Width (Bits)

Logic

Registers

Logic Cells

M9K Blocks

Memory

(Bits)

Controller

DDR2

(Half rate)

8

1,513

3,015

4

4,464

16

1,513

3,034

6

8,816

64

1,513

3,082

18

34,928

72

1,513

3,076

19

39,280

DDR2

(Full rate)

8

1,531

3,059

4

2,288

16

1,531

3,108

4

4,464

64

1,531

3,134

10

17,520

72

1,531

3,119

11

19,696

Controller+PHY

DDR2

(Half rate)

8

2,737

5,131

6

4,784

16

2,915

5,351

9

9,392

64

3,969

6,564

27

37,040

72

4,143

6,786

28

41,648

DDR2

(Full rate)

8

2,418

4,763

6

2,576

16

2,499

4,919

6

5,008

64

2,957

5,505

15

19,600

72

3,034

5,608

16

22,032