Altera DDR3 SDRAM High-Performance Controller and ALTMEMPHY IP User Manual

Page 5

Chapter 15: Introduction to ALTMEMPHY IP

15–5

Features

November 2012

Altera Corporation

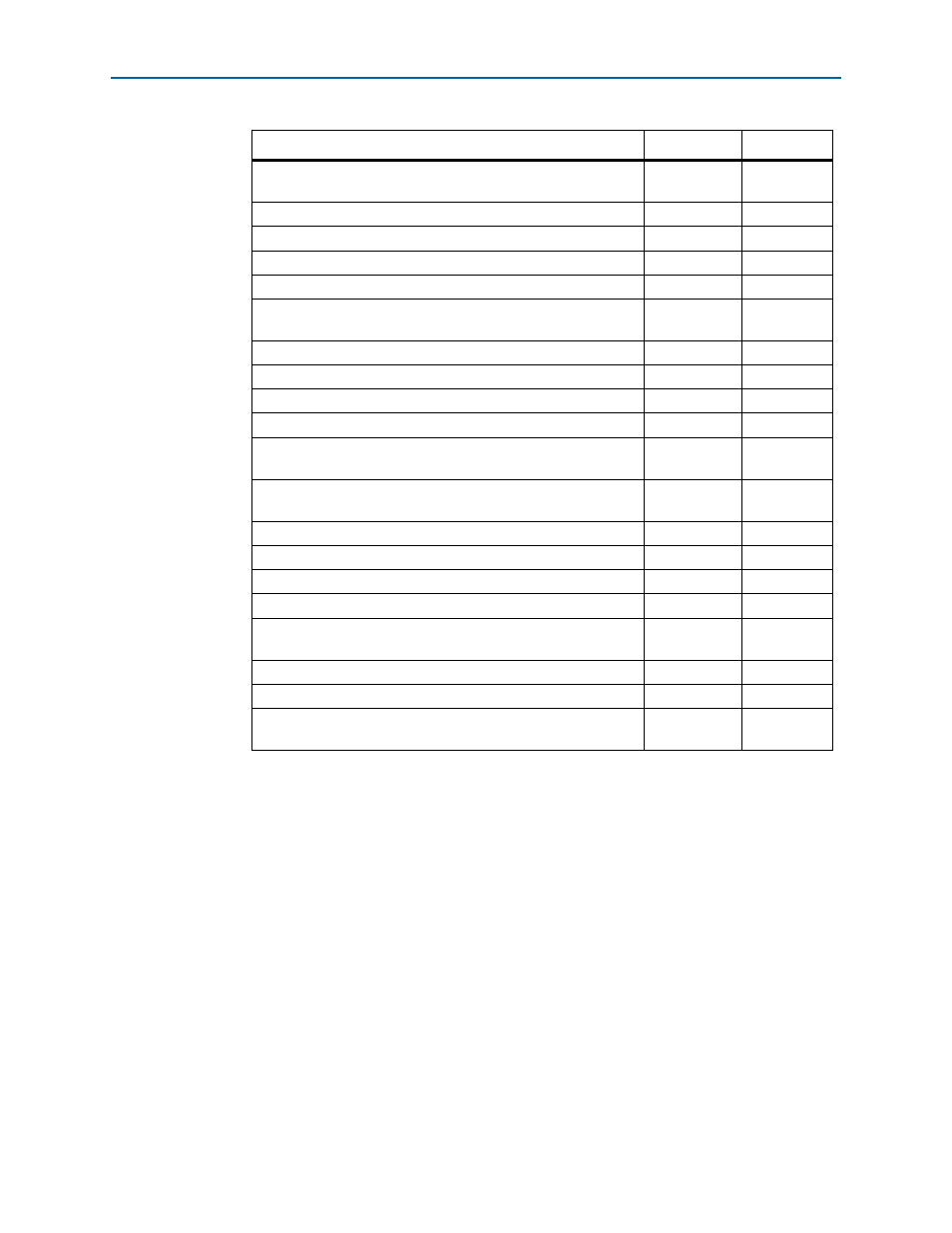

External Memory Interface Handbook

Volume 3: Reference Material

Configurable command look-ahead bank management with

in-order reads and writes

v

v

Additive latency

v

v

Support for arbitrary Avalon burst length

v

v

Built-in flexible memory burst adapter

v

v

Configurable Local-to-Memory address mappings

v

v

Optional run-time configuration of size and mode register

settings, and memory timing

v

v

Partial array self-refresh (PASR)

v

v

Support for industry-standard DDR3 SDRAM devices

Optional support for self-refresh command

v

v

Optional support for user-controlled power-down command

v

v

Optional support for automatic power-down command with

programmable time-out

v

v

Optional support for auto-precharge read and auto-precharge

write commands

v

v

Optional support for user-controller refresh

v

v

Optional multiple controller clock sharing in SOPC Builder Flow

Integrated error correction coding (ECC) function 72-bit

v

v

Integrated ECC function, 16, 24, and 40-bit

v

v

Support for partial-word write with optional automatic error

correction

v

v

SOPC Builder ready

Support for OpenCore Plus evaluation

v

v

IP functional simulation models for use in Altera-supported VHDL

and Verilog HDL simulator

v

v

Notes to

(1) HPC II supports additive latency values greater or equal to t

RCD

-1, in clock cycle unit (t

CK

).

(2) This feature is not supported with DDR3 SDRAM with leveling

.

Table 15–5. Feature Support (Part 2 of 2)

Feature

DDR and DDR2

DDR3