Features, Altmemphy megafunction, High-performance controller ii – Altera DDR3 SDRAM High-Performance Controller and ALTMEMPHY IP User Manual

Page 4

15–4

Chapter 15: Introduction to ALTMEMPHY IP

Features

External Memory Interface Handbook

November 2012

Altera Corporation

Volume 3: Reference Material

Features

ALTMEMPHY Megafunction

summarizes key feature support for the ALTMEMPHY megafunction.

In addition, the ALTMEMPHY megafunction supports DDR3 SDRAM components

without leveling:

■

The ALTMEMPHY megafunction supports DDR3 SDRAM components without

leveling for Arria II GX devices using T-topology for clock, address, and command

bus:

■

Supports multiple chip selects.

■

The DDR3 SDRAM PHY without leveling f

MAX

is 400 MHz for single chip selects.

■

No support for data-mask (DM) pins for ×4 DDR3 SDRAM DIMMs or

components, so select No for Drive DM pins from FPGA when using ×4 devices.

■

The ALTMEMPHY megafunction supports half-rate DDR3 SDRAM interfaces

only.

High-Performance Controller II

summarizes key feature support for the DDR, DDR2, and DDR3 SDRAM

HPC II.

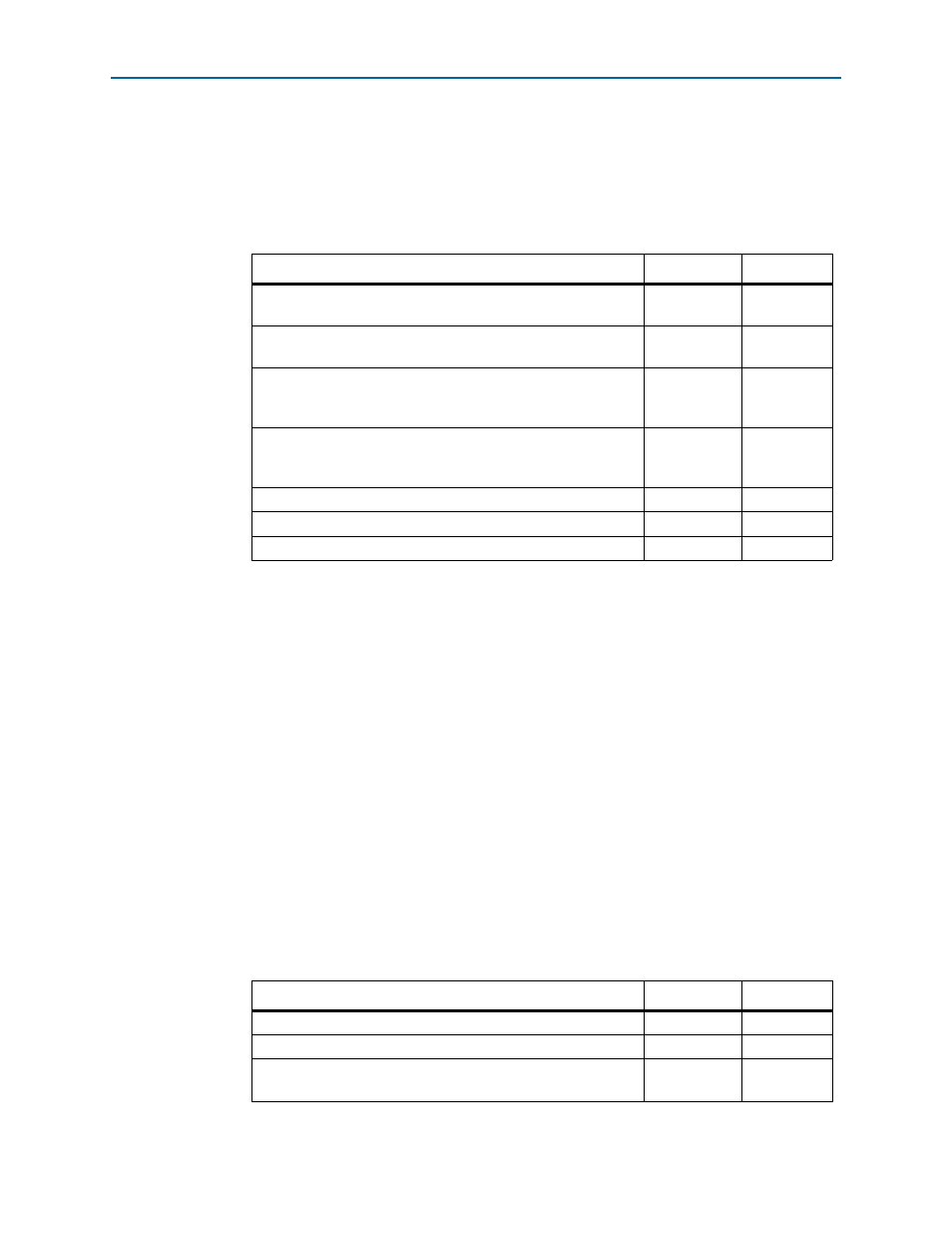

Table 15–4. ALTMEMPHY Megafunction Feature Support

Feature

DDR and DDR2

DDR3

Support for the Altera PHY Interface (AFI) on all supported

devices.

v

v

Automated initial calibration eliminating complicated read data

timing calculations.

v

v

Voltage and temperature (VT) tracking that guarantees maximum

stable performance for DDR, DDR2, and DDR3 SDRAM

interfaces.

v

v

Self-contained datapath that makes connection to an Altera

controller or a third-party controller independent of the critical

timing paths.

v

v

Full-rate interface

v

—

Half-rate interface

v

v

Easy-to-use parameter editor

v

v

Table 15–5. Feature Support (Part 1 of 2)

Feature

DDR and DDR2

DDR3

Half-rate controller

v

v

Support for AFI ALTMEMPHY

v

v

Support for Avalon

®

Memory Mapped (Avalon-MM) local

interface

v

v