Release information – Altera DDR3 SDRAM High-Performance Controller and ALTMEMPHY IP User Manual

Page 2

15–2

Chapter 15: Introduction to ALTMEMPHY IP

Release Information

External Memory Interface Handbook

November 2012

Altera Corporation

Volume 3: Reference Material

The example top-level file is a fully-functional design that you can simulate,

synthesize, and use in hardware. The example driver is a self-test module that issues

read and write commands to the controller and checks the read data to produce the

pass or fail, and test complete signals.

The ALTMEMPHY megafunction creates the datapath between the memory device

and the memory controller. The megafunction is available as a stand-alone product or

can be used in conjunction with the Altera high-performance memory controller.

When using the ALTMEMPHY megafunction as a stand-alone product, use with

either custom or third-party controllers.

1

For new designs, Altera recommends using a UniPHY-based external memory

interface, such as the DDR2 and DDR3 SDRAM controllers with UniPHY, QDR II and

QDR II+ SRAM controllers with UniPHY, or RLDRAM II controller with UniPHY.

Release Information

provides information about this release of the DDR3 SDRAM Controller

with ALTMEMPHY IP.

Altera verifies that the current version of the Quartus

®

II software compiles the

previous version of each MegaCore function. The

report any exceptions to this verification. Altera does not verify

compilation with MegaCore function versions older than one release. For information

about issues on the DDR, DDR2, or DDR3 SDRAM high-performance controller and

the ALTMEMPHY megafunction in a particular Quartus II version, refer to the

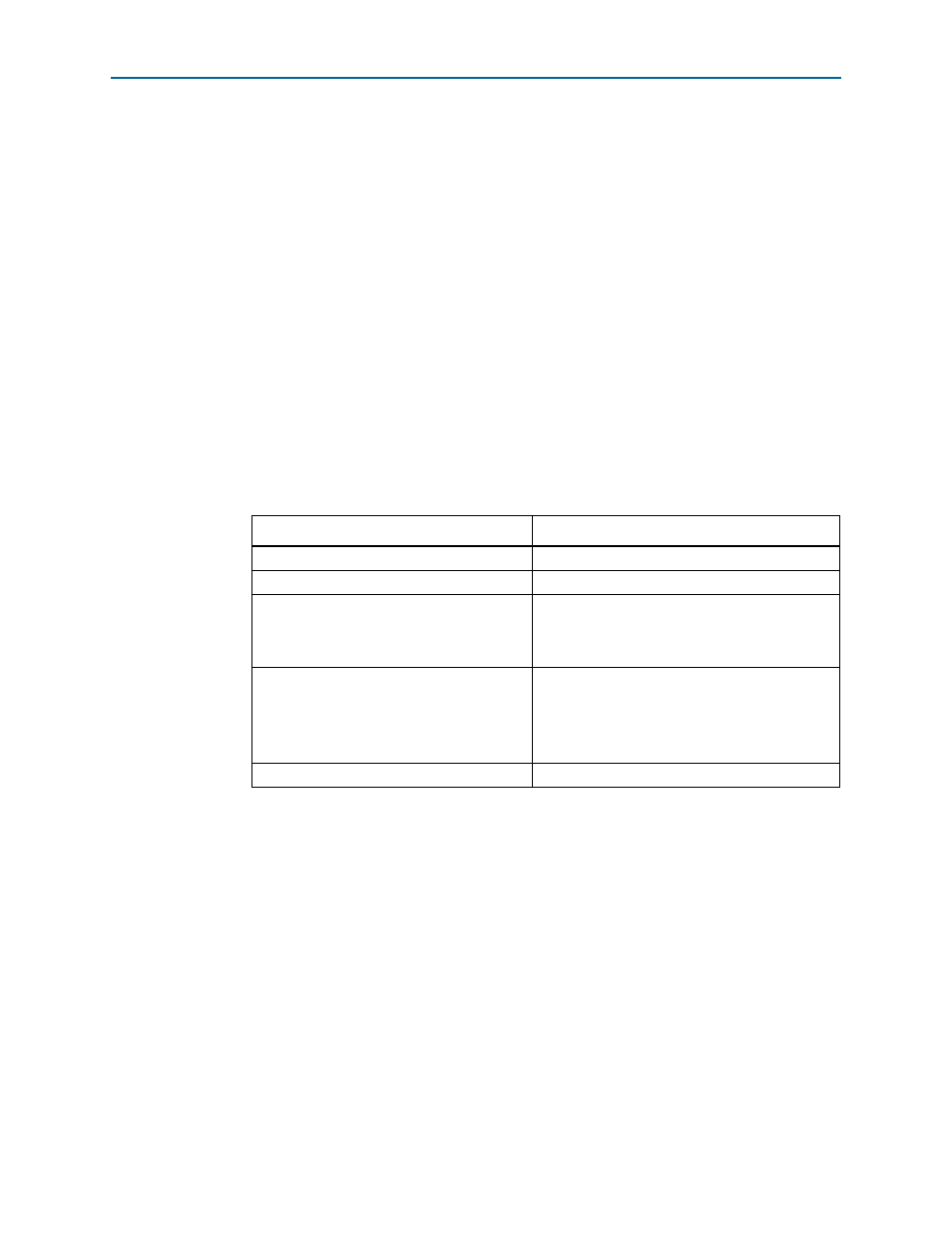

Table 15–1. Release Information

Item

Description

Version

11.1

Release Date

November 2011

Ordering Codes

IP-SDRAM/HPDDR (DDR SDRAM HPC)

IP-SDRAM/HPDDR2 (DDR2 SDRAM HPC)

IP-HPMCII (HPC II)

Product IDs

00BE (DDR SDRAM)

00BF (DDR2 SDRAM)

00C2 (DDR3 SDRAM)

00CO (ALTMEMPHY Megafunction)

Vendor ID

6AF7