Altera GPIO User Manual

Page 3

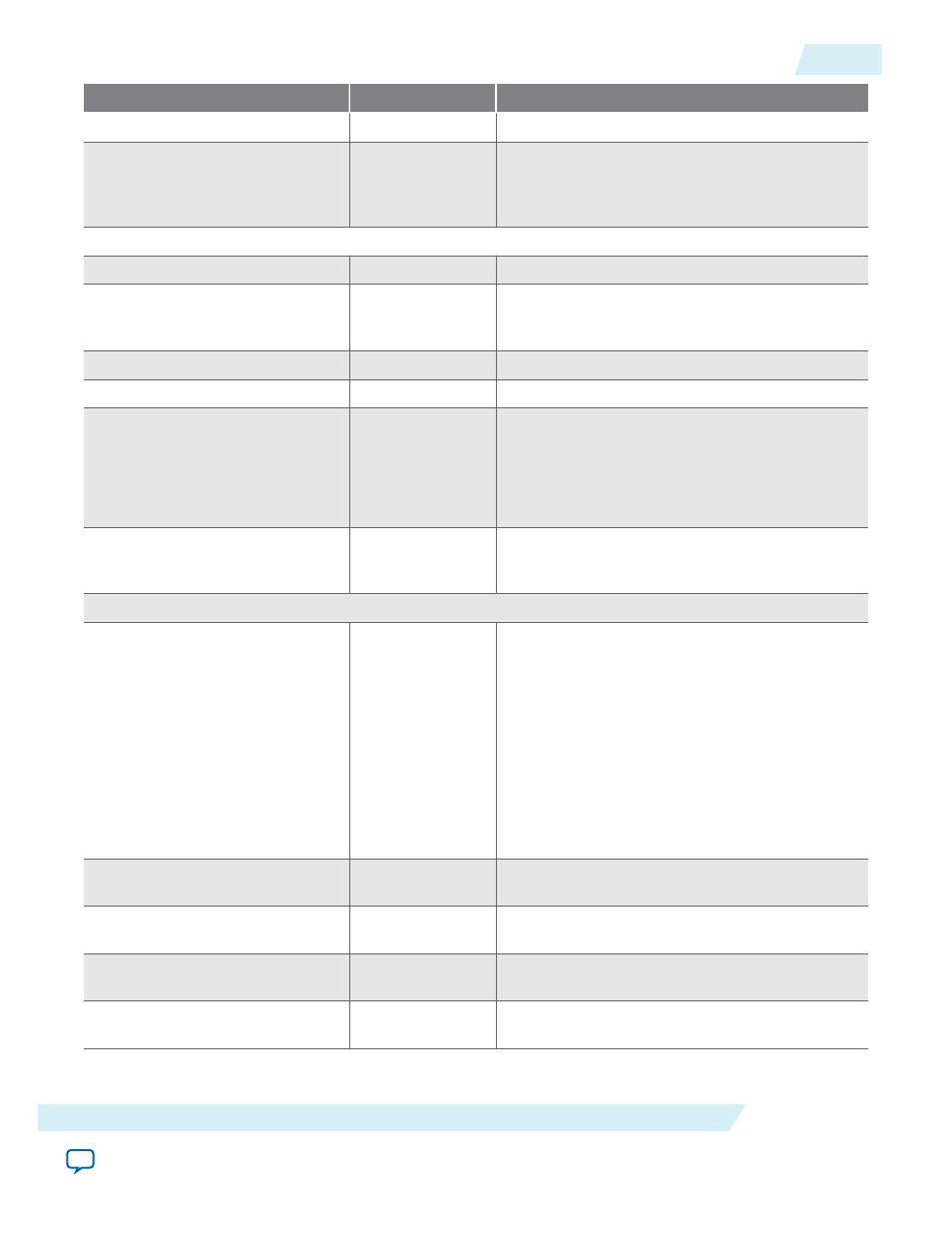

Name

Values

Description

Data width

1 to 128

Specifies the data width.

Use legacy top-level port names

Turn on, Turn off

Reverts to ports used in Arria V, Cyclone V, and

Stratix V devices. For example,

dout

becomes

dataout_h

and

dataout_l

and

din

becomes

datain_h

and

datain_l

.

Buffer

Use differential buffer

Turn on, Turn off

Allows the use of differential buffer.

Use pseudo-differential buffer

Turn on, Turn off

Allows the use of pseudo-differential buffer. This

option is only available when you enable the Use

differential buffer option.

Use bus-hold circuitry

Turn on, Turn off

Allows the use of bus-hold circuitry.

Use open-drain output

Turn on, Turn off

Allows the use of open-drain output.

Enable output enable port

Turn on, Turn off

Allows the use of OE input. This option is

available only when you set the Data Direction

option to output.

When you set the Data Direction option to

input and bidir, this option is disabled.

Enable seriestermination/

paralleltermination ports

Turn on, Turn off

Allows the use of the

seriestermination

/

paralleltermination

ports of the output

buffer.

Registers

Register mode

none, Simple

register, DDIO

This setting specifies the register mode for the

Altera GPIO IP core. The values for this

parameter are:

• none—specifies a simple wire connection

from/to the buffer.

• Simple register—specifies that the DDIO is

used as a simple register in single data-rate

mode (SDR). The Fitter may pack this register

in the I/O.

• DDIO— specifies that the IP core uses the

DDIO.

Enable synchronous clear / preset

port

None, Clear, Preset Specifies how to implement synchronous reset

port.

Enable asynchronous clear /

preset port

None, Clear, Preset Specifies how to implement asynchronous reset

port.

Enable clock enable port

Specifies whether the DDIO will have the clock

enable port exposed.

Half Rate Logic

Turn on, Turn off

Allows the Altera GPIO IP core to use half rate

logic (half-rate DDIO).

ug-altera_gpio

2014.08.18

Parameter Settings

3

Altera GPIO IP Core User Guide

Altera Corporation