Data interface signals – Altera GPIO User Manual

Page 10

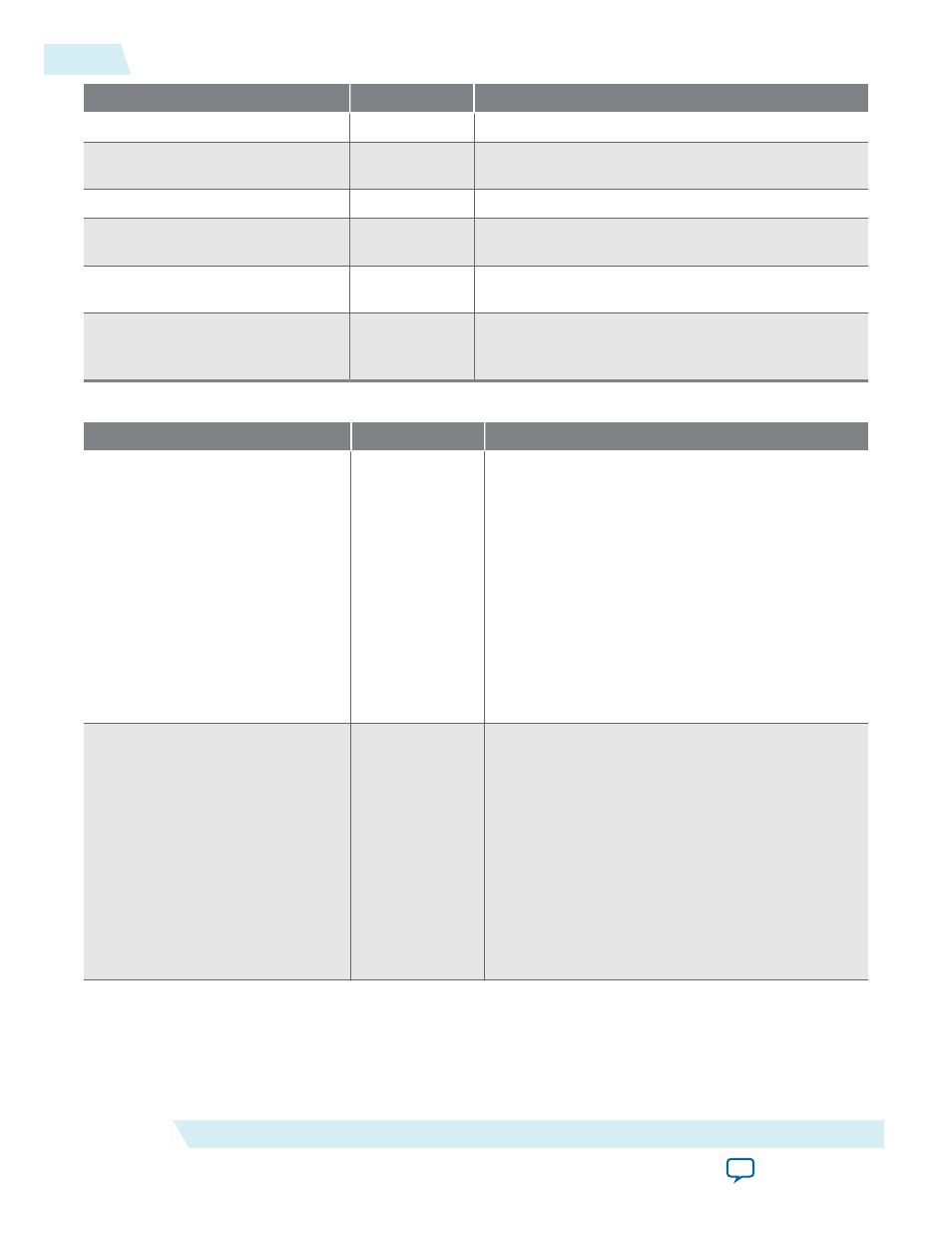

Signal Name

Direction

Description

pad_in[SIZE -1:0]

Input

Input pad port only when the input path is used.

pad_in_b[SIZE -1:0]

Input

Input negative pad port only when input path is

used, and differential buffers are enabled.

pad_out[SIZE -1:0]

Output

Output pad port only when output path is used.

pad_out_b[SIZE -1:0]

Output

Output negative pad port only when output path is

used, and differential buffers are enabled.

pad_io[SIZE -1:0]

Bidirectional Bidirectional pad port only when bidirectional paths

are used.

pad_io_b[SIZE -1:0]

Bidirectional Bidirectional negative pad port only when bidirec‐

tional paths are used, and differential buffers are

enabled.

Data Interface Signals

Signal Name

Direction

Description

din[DATA_SIZE - 1 : 0]

Input

Data connection from the core to the Altera GPIO

IP core when in output or bidirectional mode. This

interface is not present in input mode.

DATA_SIZE

has different values, depending on the

Altera GPIO configuration:

• Combinational or packed register—

DATA_SIZE

=

SIZE

• DDIO, no half-rate logic—

DATA_SIZE

= 2 x

SIZE

• DDIO with half-rate logic—

DATA_SIZE

= 4 x

SIZE

dout[DATA_SIZE - 1 : 0]

Output

Data connection from the Altera GPIO IP core to

the core when in input or bidirectional mode. This

interface is not present in output mode.

DATA_

SIZE

has different values depending on the Altera

GPIO configuration:

• Combinational or packed register—

DATA_SIZE

=

SIZE

• DDIO, no half-rate logic—

DATA_SIZE

= 2 x

SIZE

• DDIO with half-rate logic—

DATA_SIZE

= 4 x

SIZE

10

Data Interface Signals

ug-altera_gpio

2014.08.18

Altera Corporation

Altera GPIO IP Core User Guide